## Tuomas Poikela

# Readout Architecture for Hybrid Pixel Readout Chips

TURKU CENTRE for COMPUTER SCIENCE

TUCS Dissertations No 198, June 2015

## Readout architectures for hybrid pixel detector readout chips

## Tuomas Poikela

To be presented, with the permission of the Faculty of Mathematics and Natural Science of the University of Turku, for public criticism in Auditorium Beta on June 15, 2015, at 12 noon.

University of Turku

Department of Information Technology

FI-20014 Turun yliopisto

2015

## Supervisors

Adjuct Professor Juha Plosila Department of Information Technology University of Turku FI-20014 Turun yliopisto Finland

D.Sc. (Tech.) Tomi Westerlund Department of Information Technology University of Turku FI-20014 Turun yliopisto Finland

#### Reviewers

Professor Timo D. Hämäläinen Department of Pervasive Computing Tampere University of Technology PL 527, 33101 Tampere Finland

Professor Thomas Hollstein Department of Computer Engineering Tallinn University of Technology Akadeemia tee 15A, 12618 Tallinn Estonia

## Opponent

Professor Angelo Rivetti Department of Physics The Torino University Via P. Giuria, 1 - 10125 Torino Italy

ISBN 978-952-12-3235-0 ISSN 1239-1883

## Abstract

The original contribution of this thesis to knowledge are novel digital readout architectures for hybrid pixel readout chips. The thesis presents asynchronous bus-based architecture, a data-node based column architecture and a network-based pixel matrix architecture for data transportation. It is shown that the data-node architecture achieves readout efficiency 99% with half the output rate as a bus-based system. The network-based solution avoids "broken" columns due to some manufacturing errors, and it distributes internal data traffic more evenly across the pixel matrix than column-based architectures. An improvement of > 10% to the efficiency is achieved with uniform and non-uniform hit occupancies.

Architectural design has been done using transaction level modeling (TLM) and sequential high-level design techniques for reducing the design and simulation time. It has been possible to simulate tens of column and full chip architectures using the high-level techniques. A decrease of > 10 in run-time is observed using these techniques compared to register transfer level (RTL) design technique. Reduction of 50% for lines-of-code (LoC) for the high-level models compared to the RTL description has been achieved.

Two architectures are then demonstrated in two hybrid pixel readout chips. The first chip, Timepix3 has been designed for the Medipix3 collaboration. According to the measurements, it consumes < 1 W/cm<sup>2</sup>. It also delivers up to 40 Mhits/s/cm<sup>2</sup> with 10-bit time-over-threshold (ToT) and 18-bit time-of-arrival (ToA) of 1.5625 ns. The chip uses a token-arbitrated, asynchronous two-phase handshake column bus for internal data transfer. It has also been successfully used in a multi-chip particle tracking telescope.

The second chip, VeloPix, is a readout chip being designed for the upgrade of Vertex Locator (VELO) of the LHCb experiment at CERN. Based on the simulations, it consumes  $< 1.5 \text{ W/cm}^2$  while delivering up to 320 Mpackets/s/cm<sup>2</sup>, each packet containing up to 8 pixels. VeloPix uses a node-based data fabric for achieving throughput of 13.3 Mpackets/s from the column to the EoC. By combining Monte Carlo physics data with high-level simulations, it has been demonstrated that the architecture meets requirements of the VELO (260 Mpackets/s/ $cm^2$  with efficiency of 99%).

## Tiivistelmä

Tässä tutkimuksessa analysoidaan uusia digitaalisia tiedonsiirtoarkkitehtuureita hybridipikseli-ilmaisimien lukupiireille. Väitöskirja esittelee asynkronisen väylän, data-solmuihin perustuvan pystyriviarkkitehtuurin sekä verkkopohjaisen arkkitehtuurin pikselimatriisin lukuun. Tutkimuksessa näytetään miten solmupohjaisella arkkitehtuurilla voidaan saavuttaa 99% tiedonlukutehokkuus käyttäen matalampaa nopeutta kuin väyläpohjaisessa arkkitehtuurissa. Verkkopohjainen ratkaisu puolestaan lisää sietokykyä rikkinäisiä pikselipystyrivejä vastaan, ja se jakaa piirin tietoliikenteen tasaisemmin pikselimatriisin sisällä kuin pystyrivipohjaiset ratkaisut. Yli 10% parempi lukutehokkuus on saavutettu verrattuna pystyriviarkkitehtuuriin.

Arkkitehtuurin suunnittelu on tehty käyttäen TLM- ja sekventiaalisia korkean tason suunnittelutekniikoita. Käyttäen näitä menetelmiä on pystytty simuloimaan kymmeniä erilaisia pikselipystyrivi- ja koko piirin kattavia arkkitehtuureita. Simulaatioiden ajoaika on lyhentynyt yli kymmenkertaisesti näillä tekniikoilla verrattuna RTL-suunnittelutekniikkaan. Korkean tason mallit ovat noin 50% kompaktimpia koodiriveissä laskettuna.

Kahta näistä arkkitehtuureista esitellään tarkemmin kahdessa eri piirissä. Ensimmäinen piiri, Timepix3, on suunniteltu Medipix3-kollaboraatiolle. Mittausten mukaan tehon kulutus on  $< 1~\rm W/cm^2$ . Piirin lukunopeus on  $40~\rm Mpikseliosumaa/s/cm^2$ , joista jokainen sisältää  $10~\rm bitin$  varaustiedon sekä  $18~\rm bitin$  aikatiedon  $1.5625~\rm nanosekunnin$  tarkkuudella. Piiri käyttää asynkronista kaksivaiheista väyläprotokollaa sisäiseen tiedonsiirtoon. Sitä on myös onnistuneesti käytetty useammasta piiristä rakennetussa ilmaisimessa hiukkasten jäljittämiseen.

Toinen piiri, VeloPix, on Euroopan ydintutkimuskeskuksen CERNin LHCb-kokeen VELO-ilmaisimen päivitystä varten kehitetty pikselilukupiiri. Simulaatioiden perusteella piirin tehon kulutus on  $< 1.5 \,\mathrm{W/cm^2}$ . Piirin lukunopeus on 320 Mpakettia/s/cm², joista jokainen sisältää jopa 8 pikseliosumaa. VeloPix käyttää solmupohjaista arkkitehtuuria saavuttaakseen lukunopeuden 13.3 Mpakettia/s pikselipystyriviltä. Yhdistämällä Monte Carlo simulaatioden tulokset korkean tason simulaatioihin on näytetty, että arkkitehtuuri täyttää VELOn vaatimukset (260 Mpakettia/s/cm² 99%:n tiedonlukutehokkuudella).

## Acknowledgements

Although writing a thesis and getting your thoughts down on paper is sometimes a lonely road, I could not have done all the work presented here without support from family, friends and colleagues.

First and foremost, I would like to thank my supervisors Tomi and Juha at Turku for giving me this opportunity to pursue my PhD at the university of Turku, and giving me freedom to carry out the research in Switzerland at CERN. They have supported me during these years and always given me advice when needed.

I am grateful to Ken for supervising me at CERN during my thesis work, and giving me a chance to join the working community of CERN in the first place. I also want to thank him for motivating me to write when other projects seemed more interesting.

Professors Thomas Hollstein and Timo D. Hämäläinen are gratefully acknowledged for reviewing this thesis, and professor Angelo Rivetti for taking the time to be my opponent in the defense of this thesis. I also gratefully acknowledge that this thesis was funded by Turku Centre for Computer Science (TUCS) and the European Organization for Nuclear Science (CERN) Doctoral student program. EURO-DOTS is also acknowledged for giving me scholarship for PhD courses.

I would like to thank my colleagues in CERN ESE group for many lively discussions on electronics and topics completely unrelated to work as well. Thanks to Michael and Xavi for trusting in my skills and giving me the chance to work in Timepix3 project as part of my PhD. Also thanks to all the people in Medipix3 collaboration for being open to my new ideas about Timepix3. Thanks to Timepix3 readout system development team, and especially Szymon for the on-site support. Thanks to Erik for providing me Python scripts. Thanks to Jerome for helping with the Timepix3 measurement hardware. Thanks also to other colleagues in the CERN Medipix team: Massimiliano, Rafa, Winnie, Pierpaolo. Thanks to all other designers of Timepix3 for all the hard effort to make the chip work: Vladimir G, Yunan, Francesco. Thanks to Matt for many discussions on digital design. Thanks to colleagues in the LHCb VELO, especially Martin, Paula and Jan for trusting me with the VeloPix design. Thanks to Jonne for sending me

his thesis from Finland.

Thanks to all the people who have made my stay in Geneva very enjoyable and have shown there's more to do than just work: climbing buddies, bandmates, other friends and especially "perhetutut".

Thanks to my parents Maarit and Timo for their encouraging words and support throughout my life.

Above all, I am in gratitude to my wife Hanna for her support and companionship during my doctoral studies. And finally special thanks to our daughter Emilia who has brought so much joy into my life.

Geneva, May 2015

-Tuomas Poikela

## Contents

| Li | st Of | Acronyms                                                    | cvii |

|----|-------|-------------------------------------------------------------|------|

| 1  | Intr  | oduction                                                    | 1    |

|    | 1.1   | Applications of pixel detectors                             | 2    |

|    | 1.2   | Hybrid pixel detectors                                      | 4    |

|    |       | 1.2.1 Noise                                                 | 5    |

|    |       | 1.2.2 Radiation tolerance                                   | 7    |

|    |       | 1.2.3 Power                                                 | 9    |

|    |       | 1.2.4 Other types of pixel detectors                        | 10   |

|    | 1.3   | Requirements                                                | 11   |

|    | 1.4   | Scope and original contributions                            | 13   |

|    | 1.5   | Related work and background                                 | 15   |

|    |       | 1.5.1 Simulation studies                                    | 15   |

|    |       | 1.5.2 Pixel readout architectures $\dots \dots \dots \dots$ | 16   |

| 2  | Hyb   | orid pixel detector readout ASIC architectures              | 19   |

|    | 2.1   | Architecture of hybrid pixel detector ASIC                  | 20   |

|    |       | 2.1.1 Pixel matrix                                          | 20   |

|    |       | 2.1.2 Periphery                                             | 23   |

|    | 2.2   | Readout ASIC data flow                                      | 23   |

|    | 2.3   | Measuring time                                              | 25   |

|    | 2.4   | Occupancy, hit rate and output rate                         | 28   |

|    | 2.5   | Efficiency                                                  | 29   |

|    | 2.6   | Continuous and sequential readout                           | 30   |

|    | 2.7   | Full and zero suppressed readout                            | 32   |

|    | 2.8   | Readout and acquisition control with a shutter              | 32   |

|    | 2.9   | Triggered and trigger-less architecture                     | 33   |

|    | 2.10  | Readout modes                                               | 33   |

|    |       | 2.10.1 Full-frame and packet-based modes                    | 33   |

|    |       | 2.10.2 Zero-suppressed frame and hybrid mode                | 34   |

|    |       | 2.10.3 Analysis of frame-based readout mode                 | 38   |

|    | 9 11  | Comparison of zero suppression schemes                      | 39   |

|   | 2.12 | Data buffering                                                                                                                                  |

|---|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|   |      | 2.12.1 Front-end efficiency and data buffering 39                                                                                               |

|   |      | 2.12.2 Pixel column readout $\dots \dots \dots$ |

|   |      | 2.12.3 Super pixel buffering                                                                                                                    |

|   | 2.13 | Node-based data fabrics                                                                                                                         |

|   |      | 2.13.1 Linear node-based data fabric                                                                                                            |

|   |      | 2.13.2 Hierarchical node-based data fabric 53                                                                                                   |

|   | 2.14 | Network on-pixel chip                                                                                                                           |

|   | 2.15 | Previous HPD ASICs                                                                                                                              |

|   | 2.16 | Prototype chips                                                                                                                                 |

|   |      | Concluding remarks                                                                                                                              |

| 3 | Sim  | ulation of HPD ASICs 69                                                                                                                         |

|   | 3.1  | Simulation tools and methodologies                                                                                                              |

|   | 9.2  | 3.1.1 Methods in this thesis                                                                                                                    |

|   |      | 3.1.2 Methods used in related work                                                                                                              |

|   | 3.2  | Architectural Simulation                                                                                                                        |

|   |      | 3.2.1 Hit extraction and generation                                                                                                             |

|   |      | 3.2.2 Front-end pile-up                                                                                                                         |

|   |      | 3.2.3 Hit grouping and clustering                                                                                                               |

|   |      | 3.2.4 Front-end buffering                                                                                                                       |

|   |      | 3.2.5 Column bus and data fabrics                                                                                                               |

|   |      | 3.2.6 End-of-Column modeling                                                                                                                    |

|   |      | 3.2.7 Output link simulation                                                                                                                    |

|   |      | 3.2.8 Simulation benchmarking                                                                                                                   |

|   | 3.3  | Latency                                                                                                                                         |

|   | 3.4  | Power consumption                                                                                                                               |

|   | 3.5  | Simulation warm-up period                                                                                                                       |

|   | 3.6  | Concluding remarks                                                                                                                              |

| 4 | Har  | dware implementation studies of readout architectures 87                                                                                        |

|   | 4.1  | Background                                                                                                                                      |

|   | 4.2  | Digital pixel implementation                                                                                                                    |

|   | 4.3  | Architectures using shift registers                                                                                                             |

|   | 4.4  | Column bus architectures                                                                                                                        |

|   | 4.5  | Clock distribution in a column                                                                                                                  |

|   | 4.6  | FIFO implementations for storing pixel data                                                                                                     |

|   | 4.7  | Data fabric implementation                                                                                                                      |

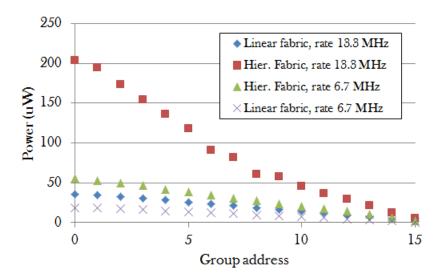

|   | •    | 4.7.1 Area and power consumption                                                                                                                |

|   |      | 4.7.2 Maximum clock frequency                                                                                                                   |

|   | 4.8  | Network implementation                                                                                                                          |

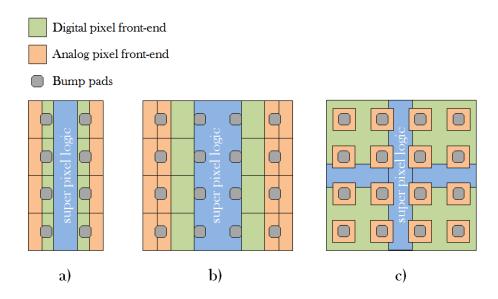

|   | 4.9  | Super pixel dimensions                                                                                                                          |

|   |      | Concluding remarks 107                                                                                                                          |

| 5 | Tim  | epix3 ASIC 109                           | 9 |

|---|------|------------------------------------------|---|

|   | 5.1  | Motivation and requirements              | 9 |

|   | 5.2  | Architecture overview                    | 1 |

|   | 5.3  | Front-end description                    | 2 |

|   |      | 5.3.1 Analog front-end                   | 2 |

|   |      | 5.3.2 Digital front-end                  | 3 |

|   | 5.4  | Super pixel                              | б |

|   |      | 5.4.1 Choice of super pixel dimensions   | 8 |

|   | 5.5  | End-of-Column and Periphery              | 0 |

|   | 5.6  | Physical implementation                  | 1 |

|   | 5.7  | Test setup                               | 5 |

|   | 5.8  | Power consumption                        | б |

|   | 5.9  | Crosstalk and digital-to-analog coupling | 7 |

|   | 5.10 | Column architecture characteristics      | 8 |

|   | 5.11 | Main limitations of Timepix3             | 1 |

|   | 5.12 | Concluding remarks                       | 2 |

| 6 | Velc | Pix ASIC 133                             | 3 |

| U | 6.1  | Motivation and requirements              | _ |

|   | 6.2  | Architecture overview                    |   |

|   | 6.3  | Front-end description                    |   |

|   | 0.0  | 6.3.1 Analog front-end                   |   |

|   |      | 6.3.2 Digital front-end                  |   |

|   | 6.4  | Super pixel                              |   |

|   | 0.1  | 6.4.1 Super pixel architecture           |   |

|   |      | 6.4.2 Choice of super pixel dimensions   |   |

|   | 6.5  | Column readout architecture              |   |

|   | 6.6  | End-of-Column and Periphery              |   |

|   | 6.7  | Monte Carlo data sets and hit generation |   |

|   | 6.8  | Architectural simulation                 |   |

|   | 0.0  | 6.8.1 Front-end pile-up                  |   |

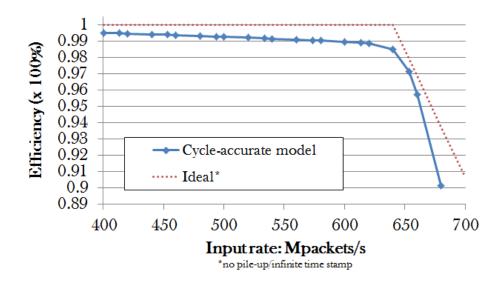

|   |      | 6.8.2 Readout efficiency                 |   |

|   |      | 6.8.3 Latency                            |   |

|   |      | 6.8.4 Model validation                   |   |

|   | 6.9  | Post-layout analysis                     |   |

|   |      | 6.9.1 Power consumption                  |   |

|   |      | 6.9.2 Timing                             |   |

|   |      | 6.9.3 Single-event upset tolerance       |   |

|   | 6.10 | Concluding remarks                       |   |

| 7 | Con | nclusions and Future Work | 159   |

|---|-----|---------------------------|-------|

|   | 7.1 | Empirical findings        | . 159 |

|   | 7.2 | Theoretical implications  | . 161 |

|   | 7.3 | Limitations of study      | . 162 |

|   | 7.4 | Future outlook            | . 163 |

## List of Figures

| 1.1  | A readout chain of a pixel detector                                   | $^{2}$ |

|------|-----------------------------------------------------------------------|--------|

| 1.2  | Two applications of pixel detectors                                   | 3      |

| 1.3  | A cross-section of a sensor and a readout chip                        | 5      |

| 1.4  | An HPD ladder consisting of $2 \times 3$ sensor and readout chips.    | 6      |

| 1.5  | Periphery and active area of a hybrid pixel sensor                    | 6      |

| 1.6  | A cross-section of an MAPS                                            | 11     |

| 1.7  | Different performance metrics for a readout ASIC                      | 12     |

| 2.1  | Structure of an HPD readout chip                                      | 21     |

| 2.2  | Pulse processing chain in an HPD readout chip                         | 22     |

| 2.3  | Data flow of an HPD readout chip                                      | 24     |

| 2.4  | Generating a global timing reference for pixels                       | 27     |

| 2.5  | A novel method for a global timing reference for pixels               | 27     |

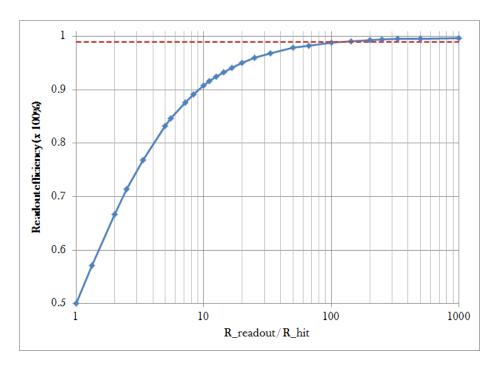

| 2.6  | Readout efficiency of a single pixel                                  | 31     |

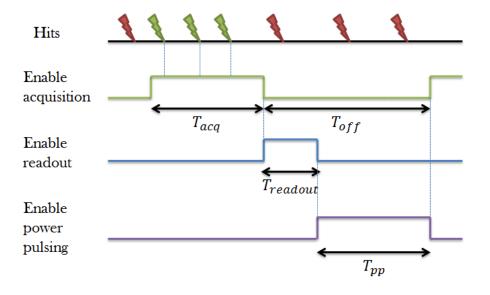

| 2.7  | Acquisition, readout and power pulsing phases                         | 31     |

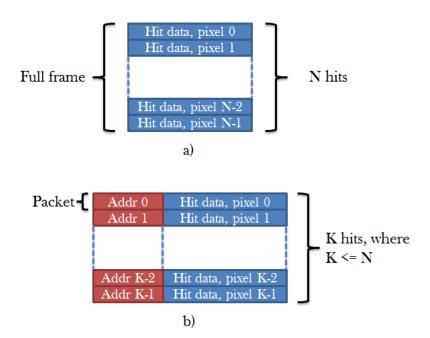

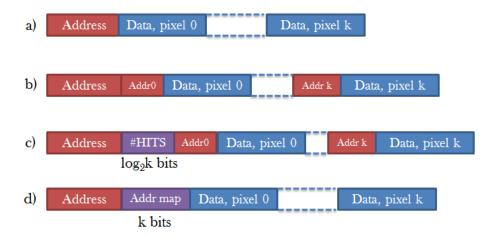

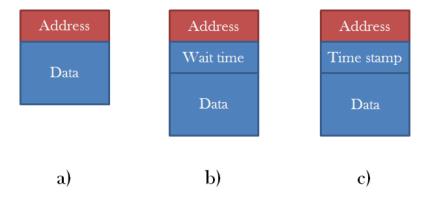

| 2.8  | Data structures for encoding pixel hits                               | 34     |

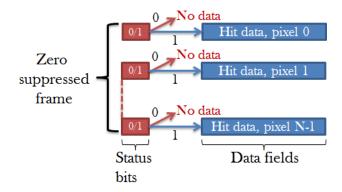

| 2.9  | Zero-suppressed frame structure for encoding pixel hits               | 35     |

| 2.10 | A hybrid data structure for encoding pixel hits                       | 36     |

| 2.11 | A zero suppression scheme for a single pixel frame                    | 37     |

| 2.12 | A zero suppression scheme for a chip periphery                        | 37     |

| 2.13 | Readout efficiency of frame-based readout                             | 38     |

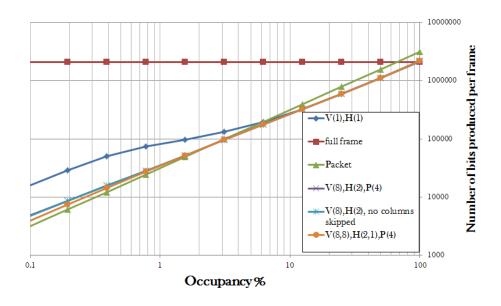

| 2.14 | Total number of bits versus occupancy                                 | 40     |

| 2.15 | A buffered system depicting a digital pixel front-end electronics.    | 40     |

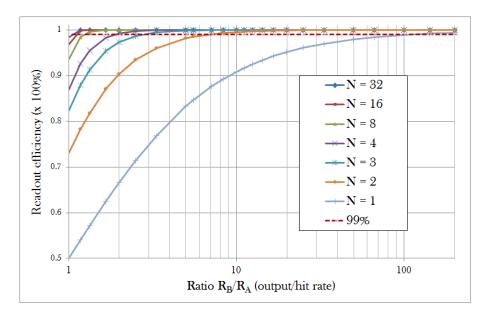

| 2.16 | Readout efficiency of a digital front-end buffer                      | 41     |

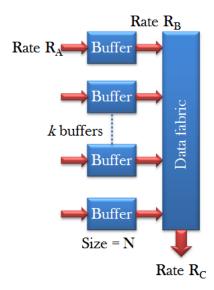

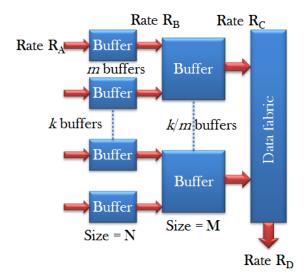

| 2.17 | Pixel buffers connected to a data transportation fabric               | 42     |

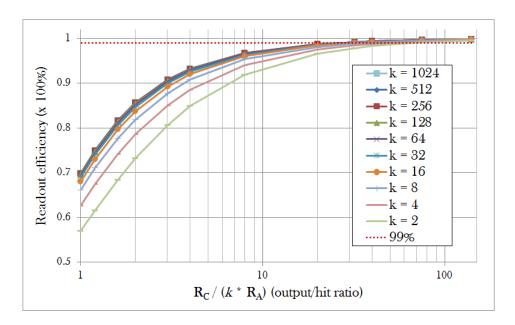

| 2.18 | Readout efficiency of a pixel column                                  | 43     |

| 2.19 | Two column arbitration schemes                                        | 44     |

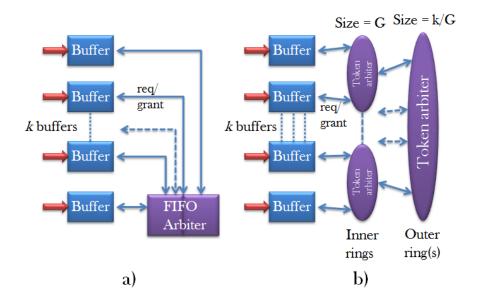

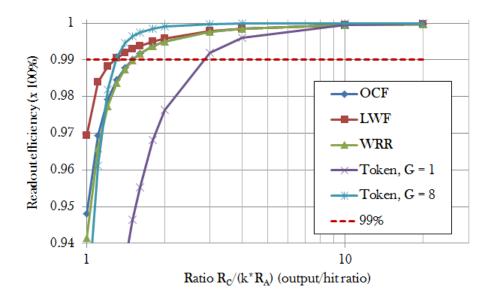

| 2.20 | Readout efficiency of a pixel column with different arbiters          | 45     |

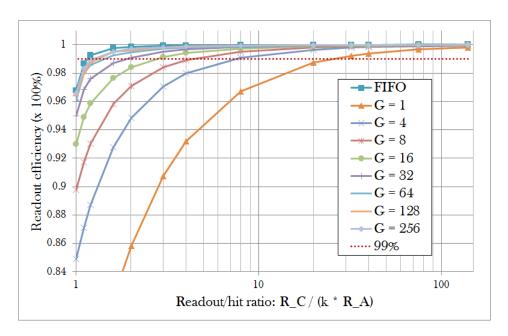

| 2.21 | A buffered system with $m$ pixels and one super pixel buffer          | 46     |

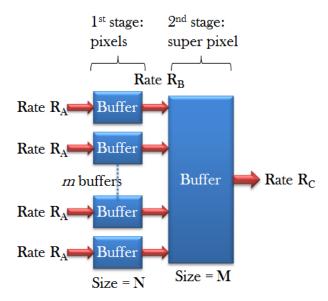

| 2.22 | Readout efficiencies with different super pixel buffer depths .       | 47     |

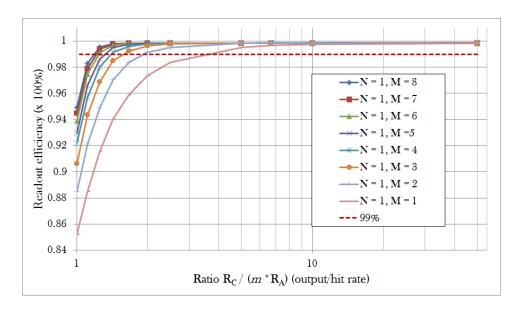

| 2.23 | A buffered system with super pixels and a data fabric                 | 48     |

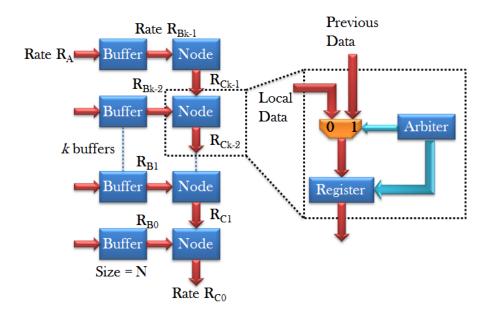

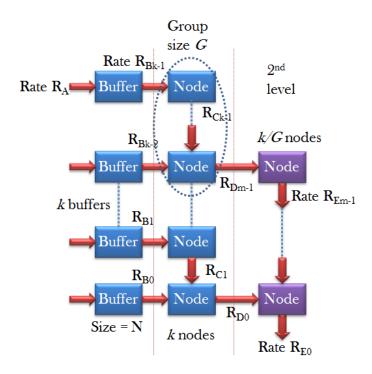

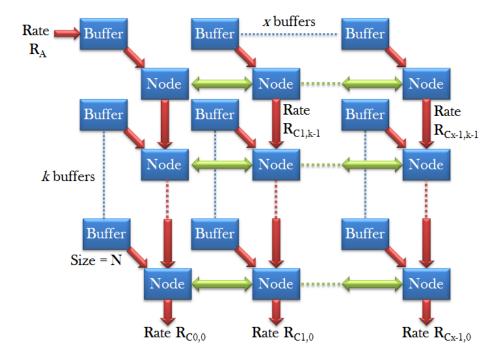

| 2.24 | A buffered data fabric with $k$ buffers (pixels), and $k$ data nodes. | 49     |

| 2.25 | The contents of a data packet for different arbitration schemes.      | 50     |

|      |                                                                       |        |

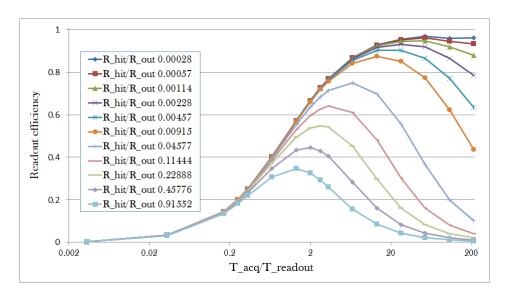

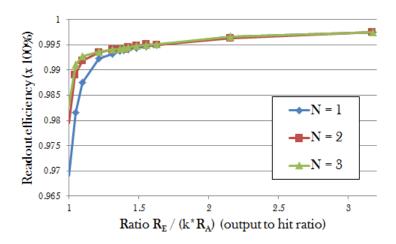

| 2.26 | Readout efficiencies of the linear data fabric                              | 52  |

|------|-----------------------------------------------------------------------------|-----|

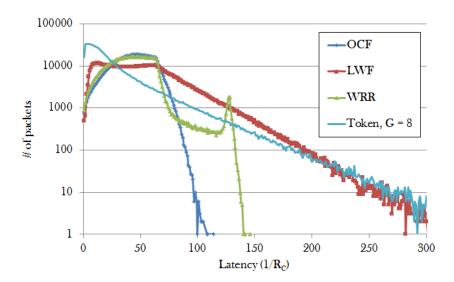

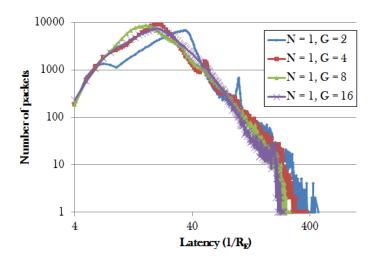

| 2.27 | Latencies of the distributed data fabric                                    | 53  |

| 2.28 | A node-based data fabric with two levels                                    | 54  |

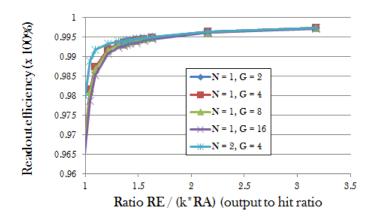

| 2.29 | Efficiencies of the hierarchical 2-level data fabric                        | 55  |

| 2.30 | Readout efficiency with varying groups for 2-level data fabric.             | 56  |

| 2.31 | The latency of packets in the two-level data fabric                         | 57  |

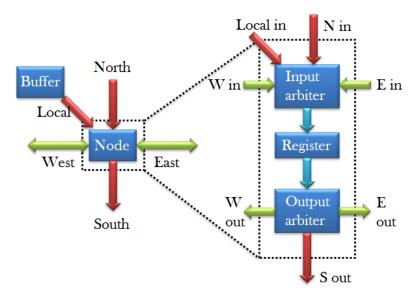

| 2.32 | A network of data nodes                                                     | 58  |

| 2.33 | A close-up of one data node of the network and a local buffer.              | 59  |

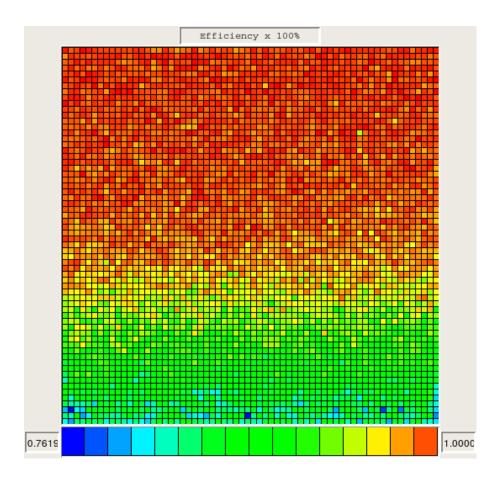

| 2.34 | Readout efficiency per data node of a $64 \times 64$ network                | 61  |

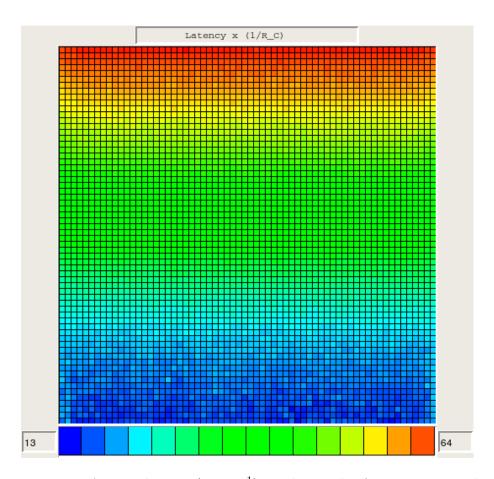

| 2.35 | Average latency (in $R_C^{-1}$ ) per data node of a $64 \times 64$ network. | 62  |

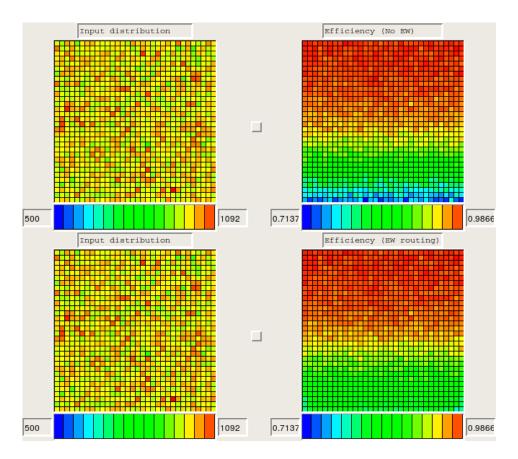

| 2.36 | Comparison of two $32 \times 32$ networks using uniform hits                | 63  |

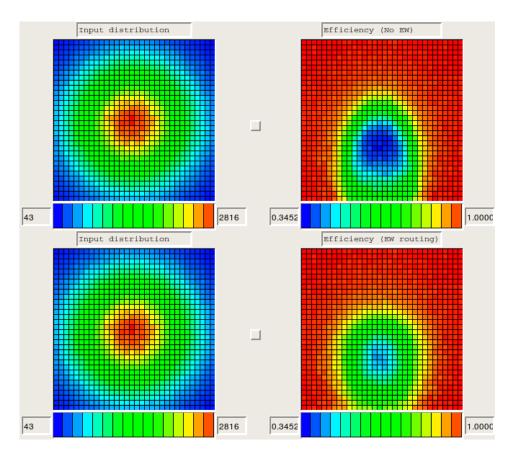

| 2.37 | Comparison of two $32 \times 32$ networks using non-uniform hits.           | 64  |

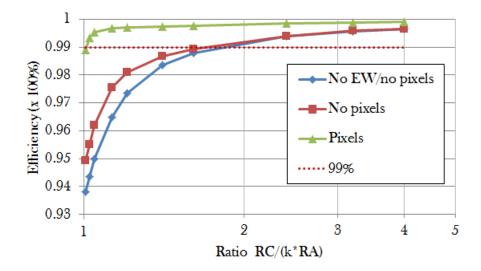

| 2.38 | Comparison of efficiency of three $64 \times 64$ networks                   | 65  |

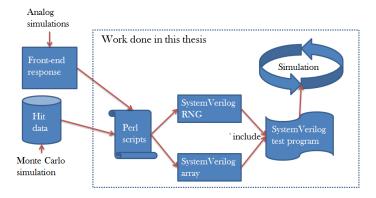

| 3.1  | The process for extracting hits for the simulations                         | 74  |

| 3.2  | A class for modeling front-end pile-up                                      | 75  |

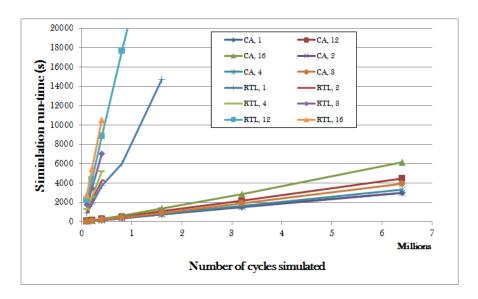

| 3.3  | Run-time of RTL and sequential cycle-accurate simulations                   | 79  |

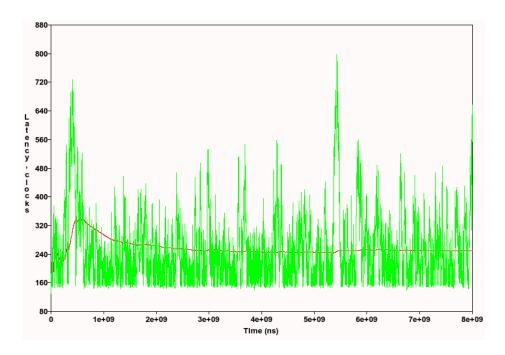

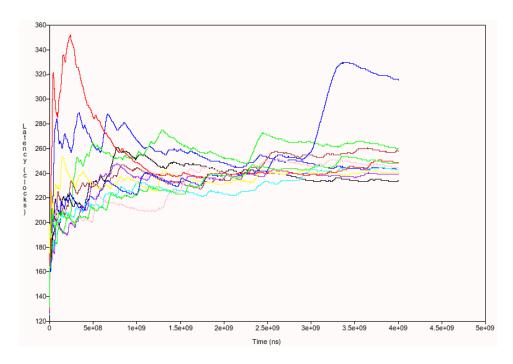

| 3.4  | CMA and average latency sampled every 1000 packets                          | 83  |

| 3.5  | CMA of latency sampled every 1000 packets                                   | 84  |

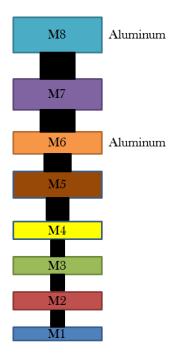

| 4.1  | The metal stack of 8 layers of the complementary metal oxide                |     |

| 4.0  | ( )                                                                         | 88  |

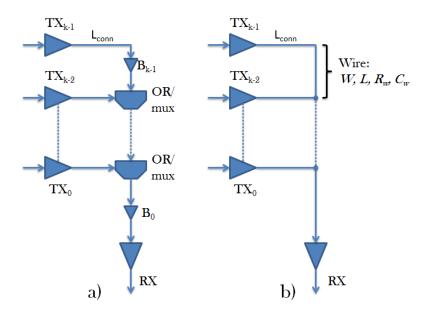

| 4.2  |                                                                             | 93  |

| 4.3  | , , ,                                                                       | 94  |

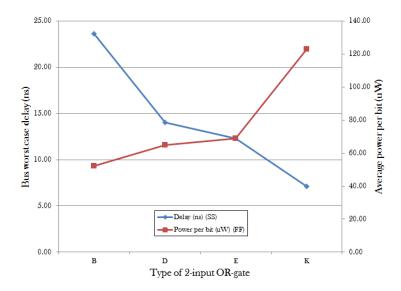

| 4.4  |                                                                             | 95  |

| 4.5  | 1                                                                           | 97  |

| 4.6  | The pin interface between two groups in the linear fabric 1                 |     |

| 4.7  |                                                                             | 02  |

| 4.8  | A layout of a network of $4 \times 4$ data nodes                            |     |

| 4.9  | Different super pixel floorplans                                            | .07 |

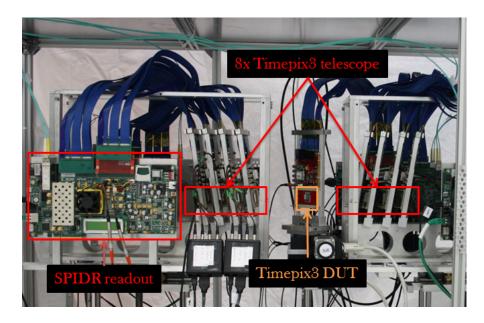

| 5.1  | An application of Timepix3 in a particle tracking telescope 1               |     |

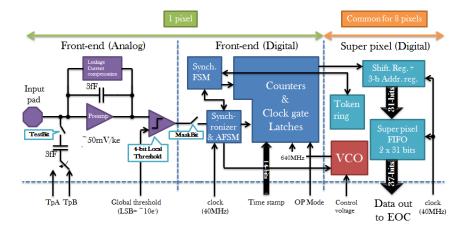

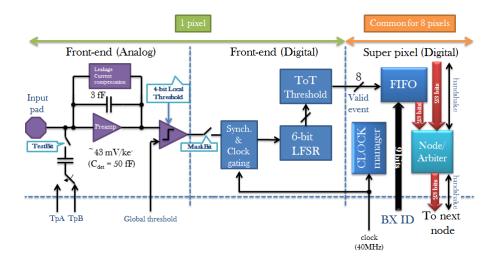

| 5.2  | A schematic of the front-end of Timepix3                                    |     |

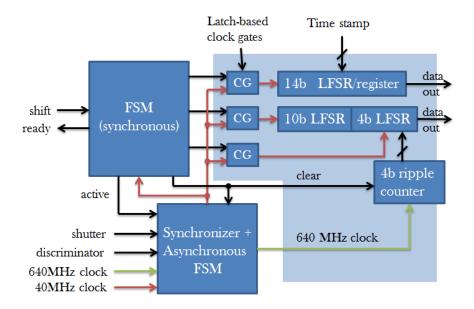

| 5.3  | A block diagram of a digital pixel of Timepix3                              | 13  |

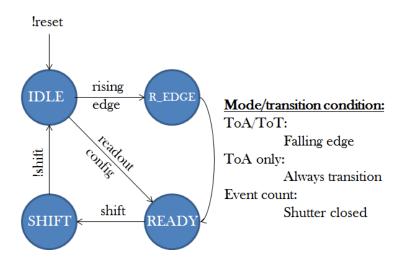

| 5.4  | Synchronous state machine of the digital front-end of Timepix3.1            | 14  |

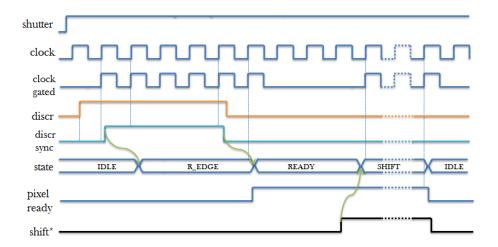

| 5.5  | Timing diagram of the digital front-end of Timepix3 1                       | 15  |

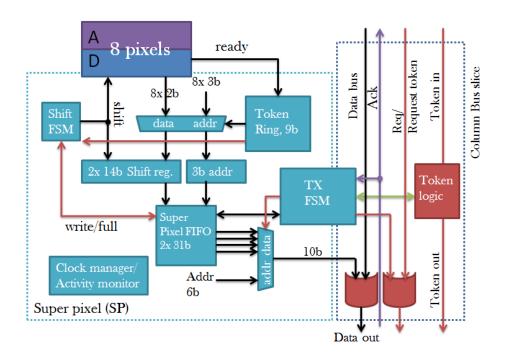

| 5.6  | A block diagram of a super pixel of Timepix3                                | 17  |

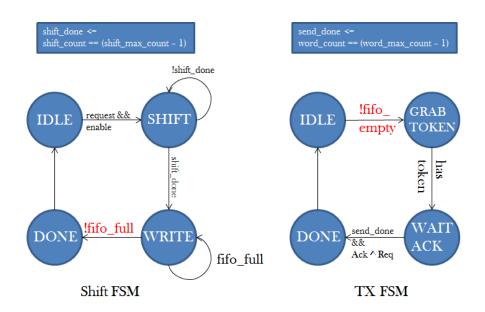

| 5.7  | State diagrams for the super pixel finite state machines (FSMs).1           | 17  |

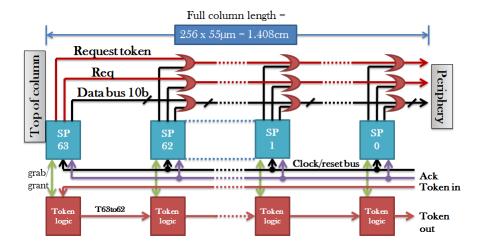

| 5.8  | A block diagram of the double column of Timepix3 1                          |     |

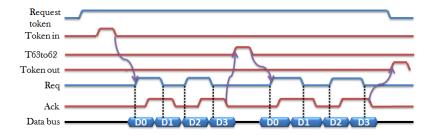

| 5.9  | Timing diagram of the column bus of Timepix3 1                              | 19  |

| 5.10 | The digital periphery of Timepix3                                           | 20  |

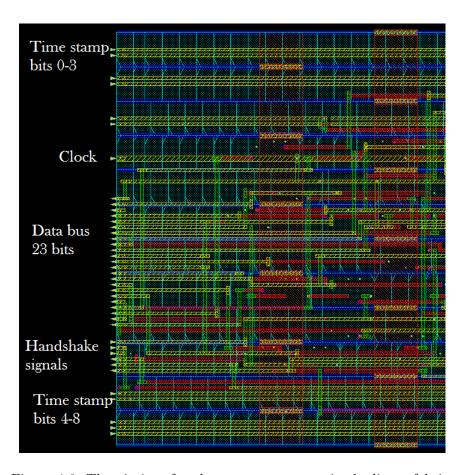

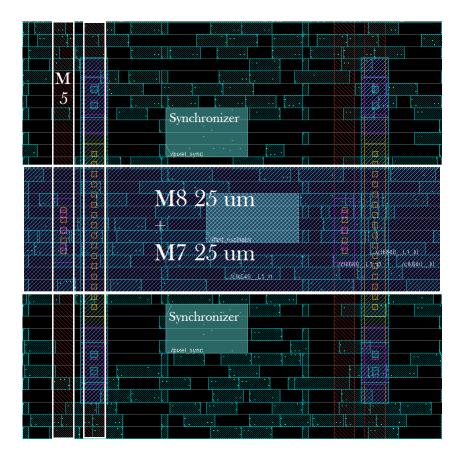

| 5.11 | The layout of the front-end synchronizer in Timepix3 1                      | 23  |

| 5.12 | The layout of a super pixel of Timepix3                                     | 24  |

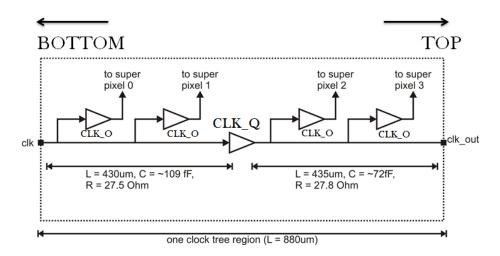

| 5.13 | A segment of the digital power distribution for a column 125        |

|------|---------------------------------------------------------------------|

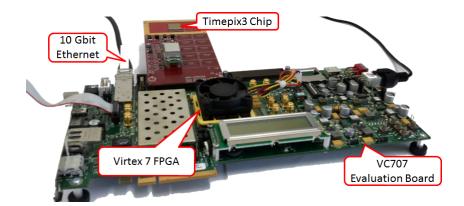

| 5.14 | The test setup used for the measurements of Timepix3 126            |

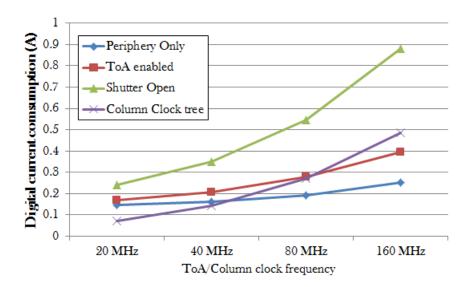

| 5.15 | Current consumption of the column clock distribution 127            |

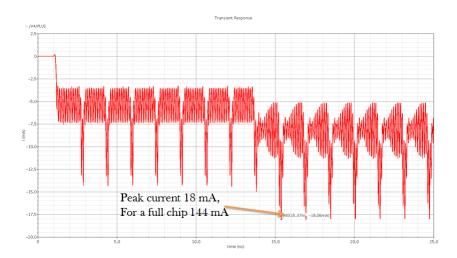

| 5.16 | The current consumption measured from the Timepix3 chip 128         |

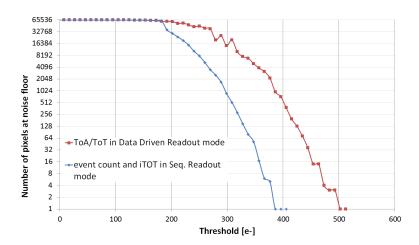

| 5.17 | The impact of the ToA counter to the minimum threshold 129          |

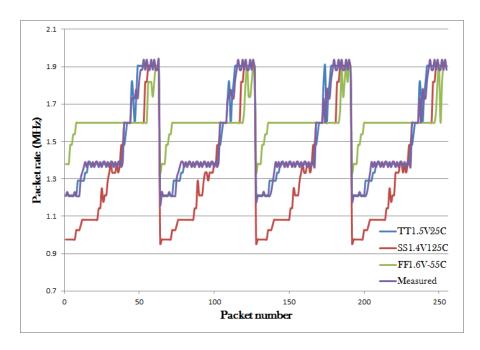

| 5.18 | Packet rates from one double column of Timepix3 130                 |

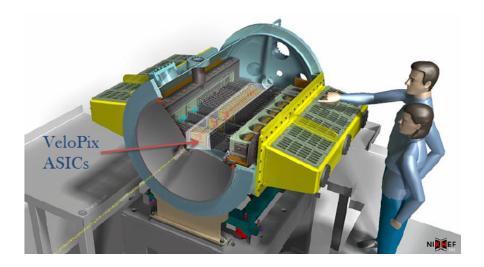

| 6.1  | Upgraded VELO detector containing 624 VeloPix ASICs 134             |

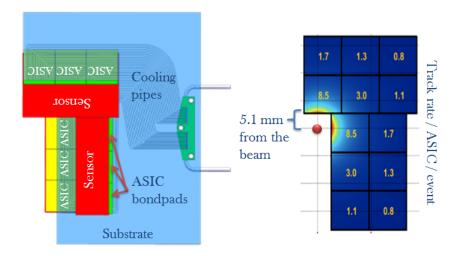

| 6.2  | A module of 12 VeloPix ASICs                                        |

| 6.3  | The block diagram of the VeloPix front-end                          |

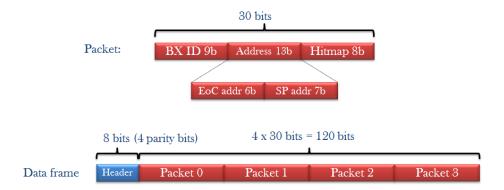

| 6.4  | The data packet and the output packet frame of VeloPix 138          |

| 6.5  | Power consumption of a super pixel of VeloPix 140                   |

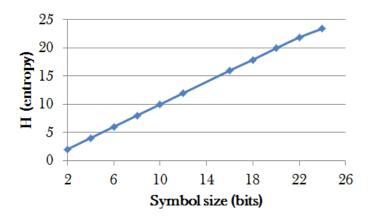

| 6.6  | Entropy of the data from VeloPix                                    |

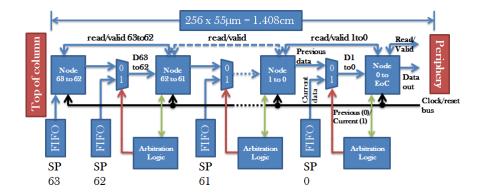

| 6.7  | A block diagram of a column architecture of VeloPix 144             |

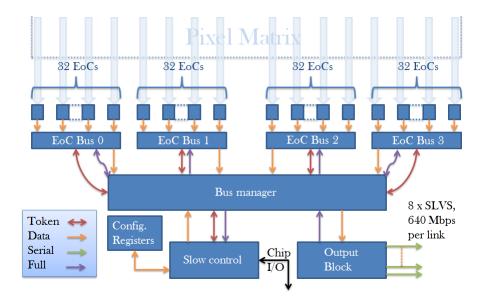

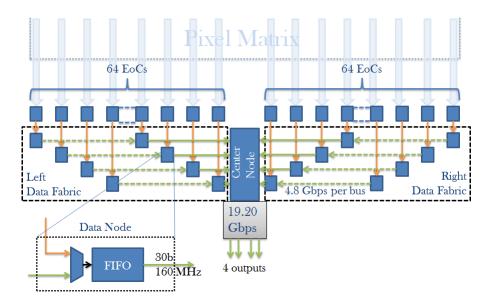

| 6.8  | The periphery data path of the VeloPix                              |

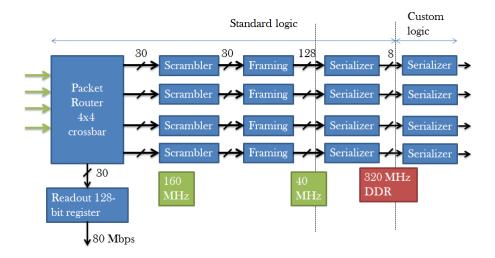

| 6.9  | The output logic of the VeloPix periphery                           |

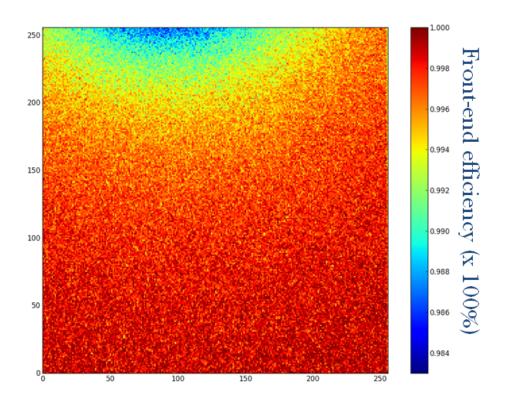

| 6.10 | Efficiency of the analog front-end                                  |

| 6.11 | Readout efficiency of the VeloPix architecture 149                  |

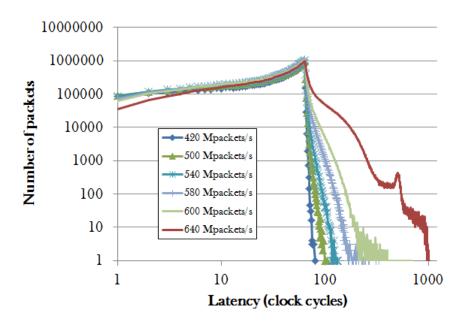

| 6.12 | Latency of the VeloPix architecture with different input rates. 150 |

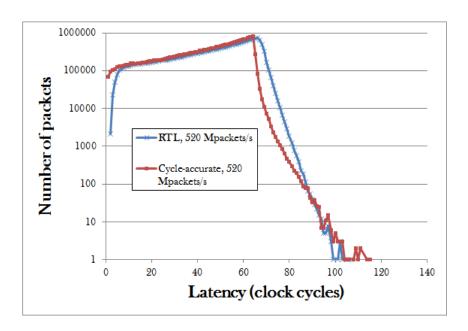

| 6.13 | Latency of the two chip models with targeted input rate $151$       |

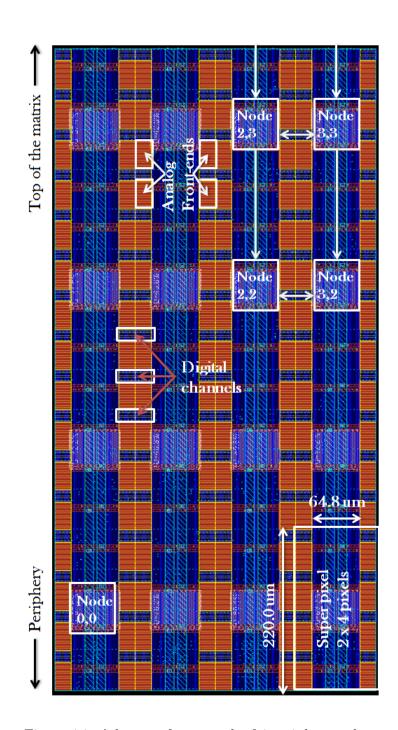

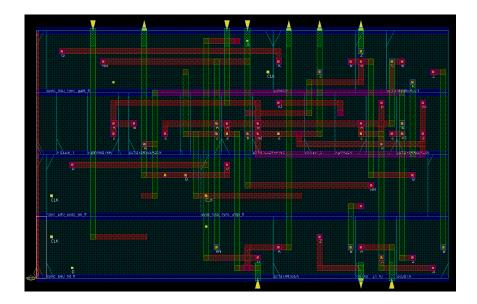

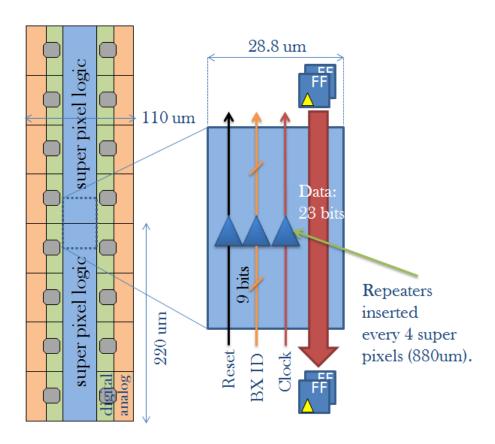

| 6.14 | A floorplan of the column of VeloPix with global signals $152$      |

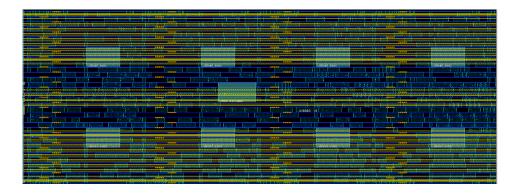

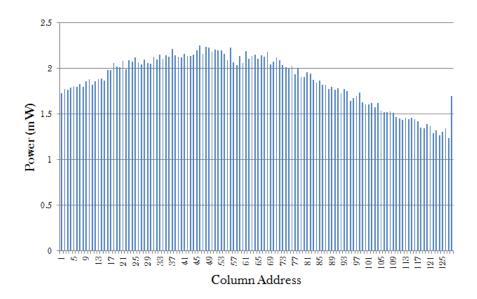

| 6.15 | Digital power consumption of the pixel matrix per column 154        |

## List of Tables

| 1.1 | General requirements for digital readout architectures                                                                                  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|

|     | HPD ASICs with time/charge measurement                                                                                                  |

|     | Transistor widths in output inverters of 2-input OR-gates 94<br>The synthesis results for the linear and hierarchical data fabrics. 103 |

|     | Timepix3 requirements                                                                                                                   |

| 6.2 | VeloPix requirements.                                                                                                                   |

| 7.1 | Summary of features in Timepix3 and VeloPix 161                                                                                         |

## List Of Acronyms

**10GbE** 10 Gb Ethernet

ADC analog-to-digital converter

AFSM asynchronous finite state machine

**ALU** arithmetic logical unit

API application programming interface

APS active pixel sensors

ASIC application specific integrated circuit

ATLAS A Toroidal LHC apparatuS

BX-ID bunch crossing identification data

**CC** Cyclomatic Complexity

**CCD** charge-coupled device

**CERN** the European Organization for Nuclear Science

CMA cumulative moving average

CMOS complementary metal oxide semiconductor

CMS Compact Muon Solenoid

**DAC** digital-to-analog converter

DC double column

**DDR** double-date rate

**DICE** dual interlocked cell

**DSP** digital signal processor

**DVFS** dynamic voltage and frequency scaling

ECC error correction coding

EDA electronics design automation

**ELT** enclosed layout transistor

ENC equivalent noise charge

**EoC** End of Column

FF fast corner

**FIFO** first-in first-out

FSM finite state machine

FPGA field-programmable gate array

GaAs gallium arsenide

GALS globally-asynchronous locally-synchronous

$\mathbf{GBE}$  gigabit ethernet

Ge germanium

**HDL** hardware description language

**HPD** hybrid pixel detector

${f IC}$  integrated circuit

${f IO}$  input-output

${f IP}$  intellectual property

**ISS** instruction-set simulator

LFSR linear-feedback shift register

LHC Large Hadron Collider

LHCb Large Hadron Collider beauty

LoC lines-of-code

LQF longest queue first

LSB least significant bit

${f LUT}$  lookup-table

LWF Longest-Wait-First

MAPS monolithic active pixel sensor

MBU single-event multiple-bit upset

MC Monte Carlo

MSB most significant bit

NoC network-on-chip

NRE non-recurring engineering

**OCF** Oldest-Cell-First

**OCV** on-chip variation

**OVM** Open Verification Methodology

PCB printed circuit board

PLL phase-locked loop

PUC pixel unit cell

PnR place and route

PVT process, voltage and temperature

RAM random access memory

**RICH** ring imaging Cherenkov

**RNG** random number generator

RTL register transfer level

RX receiver

**SCPI** standard commands for programmable instruments

SDC Synopsys design constraint

SDF standard delay format

**SEE** single-event effect

**SET** single-event transient

**SEU** single-event upset

SLVS scalable low-voltage signaling

**SNR** signal-to-noise ratio

Si silicon

SP super pixel

SPIDR Speedy PIxel Detector Readout

SPEF standard parasitic extraction format

SPP super pixel packet

SRAM static random access memory

SS slow corner

STA static timing analysis

**STI** shallow trench isolation

SV SystemVerilog

$\mathbf{TDC}$  time-to-digital converter

**TID** total ionising dose

TLM transaction level modeling

ToA time-of-arrival

ToT time-over-threshold

TT typical corner

$\mathbf{TX}$  transmitter

TMR triple modular redundancy

TSV through-silicon via

UVM Universal Verification Methodology

$\mathbf{VCD}$  value-change-dump

VCO voltage-controlled oscillator

**VELO** Vertex Locator

$\mathbf{VHDL}$  very high-speed integrated circuit hardware description language

$\mathbf{V}_t$  threshold voltage

${f VLSI}$  very large scale integrated

$\mathbf{WRR}\,$  weighted round-robin

## Chapter 1

## Introduction

Imaging sensors are being integrated into many applications due to CMOS scaling and cheapening manufacturing of integrated electronics. One type of sensor, a pixel sensor, is used in digital cameras [1] and applications requiring dynamic vision [2]. Other fields like dosimetry [3] and medical imaging [4] are starting to use CMOS circuits more widely than before. Other emerging applications for pixel sensors are artificial retina prostheses [5], for example.

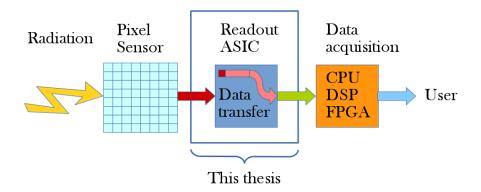

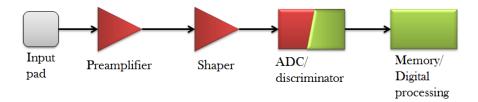

A typical readout chain for a pixel detector system is shown in Figure 1.1. In pixel sensors, incident radiation, such as X-ray photons create small charge signals in a sensitive volume sub-divided into regularly-spaced elements called pixels. The positional information of the incident particle is thus given by the address of the pixel(s) containing signal. This allows the formation of an image. Enhancements can be made using, for example, the amplitude of the signal or counting the number of signals during exposure.

Pulses from a sensor are amplified and digitized using a dedicated readout chip. In the case of a monolithic detector, the same chip functions as a sensor and a readout chip. Due to increasing demands for more information per pixel and higher signal rates together with strong constraints on power consumption, an efficient architecture is required to extract the digitized data. This thesis looks for novel solutions for transporting data from pixels to the output of the readout chip within an imaging sensor readout application specific integrated circuit (ASIC). The focus is solely on the internal readout architecture of a readout ASIC. As an additional restriction, these architectures must be able to provide timing information with sufficient accuracy attached to all data while keeping the pixel size as small as possible. Each digitized pixel hit can consist of address bits only, for example 16 bits per hit for  $256 \times 256$  pixels, or it can contain digitized time and charge information in addition, for example. This can increase the total number of bits per digitized hit to over 50.

After the digitized data has been transported from the pixels to the

Figure 1.1: A readout chain of a pixel detector.

output of the readout chip, it is transmitted off-chip for further processing. This processing can be done by a field-programmable gate array (FPGA) or a digital signal processor (DSP) or even a standard off-the-shelf microprocessor. It is also possible to connect multiple sensor/readout ASIC pairs to one data acquisition system. Finally, the data is presented to a user of the application for analysis or inspection. The user can be either another machine or a human. An example of the first one is an automatic alarm system which makes a decision to sound an alarm based on the data coming from a data acquisition system, which in turn receives its data from a readout chip connected to a light-sensitive sensor.

## 1.1 Applications of pixel detectors

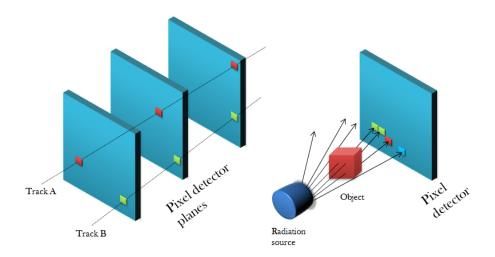

Two possible applications for pixel detectors are shown in Figure 1.2. In tracking applications, detectors are used for measuring the position and time when a particle passes through a pixel. Track reconstruction always requires more than one plane of pixels. In Figure 1.2, on the left side two different tracks captured by pixel detectors are shown. Tracks A and B can occur at different times or at the same time. By recording time information relative to a common reference in addition to pixel coordinates, tracks can be correlated with particular discrete events in time. These tracks can originate from an event which is typically a collision of particles in a high-energy physics experiment, such as protons, or atoms such as lead. Incident particles registered by tracking detectors are usually decay products of other particles, thus tracking information is used for reconstructing the patterns of decay sequences.

On the right side of Figure 1.2, an imaging application using a pixel detector is shown. The detector is used to capture energy information about

Figure 1.2: Two applications of pixel detectors: Tracking (on the left) and object imaging (on the right).

particles emitted by a radiation source. An object between the source and the detector absorbs part of the energy of a particle depending on the thickness and material of the object. Pixels shown in different colors will capture different amount of charge, and this charge information can be used to reconstruct the image. Using this method, it is possible to determine material inside the object, for example. One of the main differences between tracking and imaging applications is, that while tracking focuses on individual particle tracks, in imaging the image can be formed by integrating several tracks in a single pixel. Thus, in a tracking application, it can be beneficial to transfer hit data off a readout ASIC as quickly as possible, whereas in an imaging application data can be accumulated at the pixel-level for longer periods of time.

Pixel detectors have been used for tracking at the European Organization for Nuclear Science (CERN) in large applications such as Compact Muon Solenoid (CMS) [6] and A Toroidal LHC apparatuS (ATLAS) [7]. Large Hadron Collider beauty (LHCb) also uses pixel detectors in its ring imaging Cherenkov (RICH) detector [8], and pixels are being investigated as a detector option for the VELO detector [9] of the LHCb upgrade [10]. These applications typically require tracking precision down to a few microns and pixel sizes of a few tens of microns. As these applications operate in an environment with radiation levels orders of magnitude higher than background radiation, the choice of a type of pixel detector is also important, as will be discussed later. This thesis focuses solely on readout architectures of ASICs used in tracking applications.

#### 1.2 Hybrid pixel detectors

The focus of this thesis is on digital data readout architectures of ASICs for a particular type of pixel detectors called hybrid pixel detectors (HPDs). An HPD consists of two distinct chips called a sensor and a readout chip. Both chips can be manufactured using different processes and optimized separately, with the readout chip being generally fabricated in standard CMOS process. The sensor chip is also a solid-state device, manufactured using a semiconductor as the sensor material. Typical materials for sensors are silicon (Si), germanium (Ge), gallium arsenide (GaAs) and diamond. Semiconductor materials are self-supporting structures (unlike gas sensors, for example), have an average energy of 3.6 eV for creating an electron-hole pair and the signal is collected in the order of 10 ns [11].

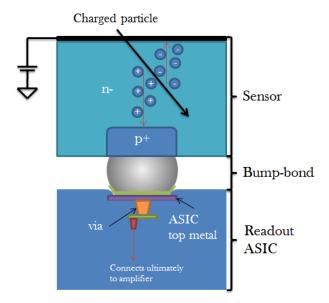

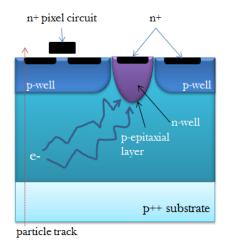

A cross-section of an interconnected sensor and a readout ASIC is shown in Figure 1.3. When a charged particle passes through the sensor, it creates electron-hole pairs inside the sensor. The number of pairs depends on, for example, the ionisation energy of the material, the energy of the incident particle and the length of its path in the material. By applying a bias voltage across the sensor, an electric field is created which causes electrons to drift from lower potential to higher. Respectively, it causes holes to drift towards lower potential and then being collected by the p+-region. As can be seen from Figure 1.3, a p-n diode is used for collecting the signal inside the sensor. It is a reverse-biased diode with fully depleted region. Typical signal magnitude is 23000 electrons for a silicon of 300  $\mu$ m [12]. Another value given in the literature is 20000 electrons or holes per 250  $\mu$ m in a fully depleted silicon sensor, corresponding to an input charge of about 3 fC [13].

Multiple pixels can receive a signal from one particle if it crosses several pixels due to low incident angle. This effect, which creates a cluster of pixels associated with one particle only, is called charge sharing. Charge sharing is useful in tracking applications for finding a more precise location of the track. By measuring the amount of charge in each pixel of the cluster and taking, for example, center of the mass of these charges, improved spatial resolution can be achieved. Without any charge information, the resolution is given by  $\frac{p}{\sqrt{12}}$  [12] for square pixels with a pitch of p. The drawback of charge sharing is that the signals per pixel are smaller in amplitude because the charge is split among several pixels and hence are more difficult to detect.

The p-n diode structure inside the sensor is connected to an interconnection between the two chips. This interconnection between the sensor and the readout chip is also called a bump-bond, and the chips are connected together using a solder process called bump-bonding [14]. The bump is connected to the readout ASIC and ultimately to the front-end electronics via the full CMOS metal stack. The purpose of the front-end electronics is to amplify and digitize signals generated by charged particles in the sensor.

Figure 1.3: A cross-section of a sensor and a readout chip connected with a bump-bond.

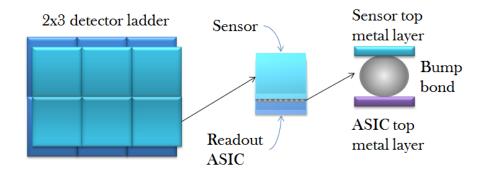

Figure 1.4 shows an example of a hybrid pixel detector of multiple chips. As mentioned, the sensor chip is mounted on top of the readout chip using bump-bonds. These bumps form the electrical connection between the two chips. Connections from readout chips to a readout system are omitted for clarity. These connections can be made using a technique called wirebonding or by using connections on back-side of the chip by deploying a redistribution layer [15].

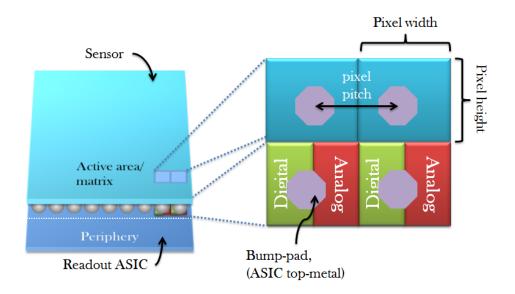

A readout chip of a pixel sensor typically has a pixel area called the pixel matrix and a peripheral area. This division is shown in Figure 1.5. The sensor is located on top of the active area and the periphery extends over the sensor edges. Pixels inside the readout chip are occupied always by analog signal processing functions and often digital logic. Analog processing is required to convert signals from a sensor to full CMOS voltage levels. The area available for electronics is constrained by the sensor pixel size. This often introduces conflicting requirements between tracking precision (smaller pixels are better) and functionality (larger pixels allow more electronics).

#### 1.2.1 Noise

Both the sensor and the readout ASIC introduce noise into the system. A leakage current in the sensor causes a signal to be generated even in the absence of an incident particle. The most important contribution to the leakage current is given by thermal generation at the surface of the device

Figure 1.4: An HPD ladder consisting of  $2 \times 3$  sensor and readout chips.

Figure 1.5: Periphery and active area of a hybrid pixel sensor and a close-up of two sensor pixels and two readout pixels.

and in the depleted volume of the sensor [12].

The leakage current of the sensor adds shot-noise to the signal which is presented to the readout electronics. A leakage current compensation circuitry can be implemented inside the readout ASIC by placing a current source or sink, depending on signal polarity, between input and output of a low-noise amplifier in the front-end [12].

The readout ASIC itself has several sources of noise. Cross-talk from digital logic to analog is a contributor to the noise of the analog front-end. This can be caused by direct capacitive coupling of frequently switching digital signals or indirect coupling via digital power supply or ground bounce through a silicon substrate. Because signals that can be detected by the analog front-end may be only 400-500 electrons in magnitude [16] or even smaller, the analog front-end is very sensitive to noise coming from the digital logic. In fact, extra noise injected into the analog front-end will increase the minimum detectable charge. The extra noise manifests itself as extra pixel hits which are not caused by signals coming from a sensor but from the readout ASIC itself. A typical measurement unit of noise for HPD systems is equivalent noise charge (ENC) which indicates a point where signal-to-noise ratio is equal to 1 [17].

For timing measurements, the rise time of a front-end amplifier combined with the signal-to-noise ratio determines the timing jitter of the system [17]. A quantization error occurs when the analog signal is converted into a discrete, digital value. This error is simply the difference of the actual analog value and the digitized value. This error is present, for example, when charge of a particle or time of arrival are measured using a sampling clock. The clock distribution itself also contributes to the quantization error because the clock signal cannot be distributed across the full chip in zero time thus arriving to different pixels at different times.

#### 1.2.2 Radiation tolerance

HPDs are often used in environments with significant levels of background radiation such as particle physics experiments. This radiation can potentially affect the readout and sensor chips. Radiation effects in electronics are usually divided into total ionising dose (TID) and single-event effects (SEEs). TID is an accumulating effect which becomes worse the longer a device is exposed to ionising radiation. The leakage current of the device increases due to charge trapped inside the shallow trench isolation (STI) oxide. Even if the device is turned off, this charge can create a leakage current path from drain to source. For 130 nm CMOS technology, this current has been measured to be less than 1  $\mu$ A per transistor [18]. The current driving capability of transistors decreases, partly due to an increase in the threshold voltage (V<sub>t</sub>) of transistors, partly due to decrease in transcon-

ductance of transistors [19]. A study on a 65 nm CMOS technology shows that PMOS transistors are particularly vulnerable to such an effect [19]. However, effects of radiation in 130 nm CMOS are well-understood and the technology shows an improvement in radiation tolerance when compared to older technologies [18]. In this thesis, 130 nm CMOS technology is used for implementing circuits. As discussed in [20], a commercial 130 nm CMOS technology is sufficiently tolerant against TID effects even when using linear transistors instead of enclosed layout transistors (ELTs) which take up more area. ELTs are typically used to improve the radiation tolerance of transistors.

An SEE is the result of an instantaneous impact of radiation affecting the state of the electronics, and can occur either as a single-event transient (SET) or a single-event upset (SEU). The former causes a transient change of voltage in one of the capacitive nodes of a logic gate or a memory cell. The likelihood of an SET decreases with increasing node capacitance. If this change is captured by a memory device, it becomes a persistent effect. On the other hand, an SEU directly causes a memory element such as a flip-flop to invert its state. Unless the device is self-correcting, a new state will persist until a new value is written into the memory device. The new state will also propagate to all the logic connected to the fan-out of this device. Mitigation techniques for SEUs will be discussed later in this thesis. Other effects such as single-event latch-up or transistor gate rupture can also be caused by radiation. However, no evidence of gate ruptures has been observed in 130 nm CMOS [21] during irradiation.

Bonacini et. al. [22, 19] have studied SEUs in 65 nm and 90 nm CMOS technologies. It has been concluded that the probability of an SEU in a single device decreases as transistor size is decreased. Although smaller devices have less capacitance, the probability of hitting a sensitive node in the device is also smaller. On the other hand, the number of devices on a single chip also increases so the probability of the SEUs across the whole system does not decrease or increase significantly due to CMOS scaling.

Design techniques such as triple modular redundancy (TMR) [23] and error correction coding (ECC) can be used to make circuits very tolerant to SEEs. TMR is based on triplicated logic in which the correct result is a vote of the three outputs. If only one device has been upset, the output of the voting is still correct. ECC such as Hamming coding can also be used to correct single-event upsets or even detect multiple bit upsets. These techniques, however, introduce area, power and timing penalties. Veeravalli [24] reports 202% - 208% area overhead when using TMR for a 32-bit arithmetic logical unit (ALU). It also reports 148% overhead for an ALU using ECC. Generally it can be concluded that for a fully triplicated design, the area overhead is always more than 200% as voting logic is required in addition to the triplication overhead. Another useful property of these

techniques is that they can also be used to improve the yield. In a case where the chip has a manufacturing error in one of the protected nodes or memories, the logic will still function correctly but the SEE tolerance is lost.

#### 1.2.3 Power

Optimization of power in an HPD readout ASIC is important for two following reasons. Firstly, the material placed in front of a detector needs to be minimized to distort the measurement as little as possible. When heavy materials are placed on the tracks of particles, part of their energy gets absorbed by the material and their trajectory can be perturbed. This prevents usage of large heat sinks for cooling, for example. Additionally, if the temperature of the readout ASIC increases, this increases leakage current and electromigration within the chip. This may make the chip slower and decrease the life-time of the device.

Secondly, due to geometry of the readout ASIC, power is brought into the chip from the periphery. Power distribution for the pixel matrix must be done from the periphery to the top of the chip. This results in long metal wires having significant resistance. For example, a 1.4 cm long copper line in 130 nm CMOS with a width of 25  $\mu$ m has a resistance of around 4 ohms. This puts a limit on the maximum amount of static and dynamic current that can be drawn before the voltage drops have an impact on the operation of transistors.

The power consumption of the readout ASIC can be divided into analog and digital power consumption. Most of the power consumed by analog electronics is typically static power [25]. There are also architectures with dynamic components [26], mainly dynamic comparators that can be clocked. Using more power at the analog front-end makes the front-end faster and improves the timing resolution, but it also introduces more noise into the front-end.

The digital power consumption is a sum of leakage power (static) and switching activity (dynamic). Each of these elements can be optimized independently of each other, and the optimization depends on operation conditions such as temperature and the expected activity in the application. The leakage can be reduced by decreasing the power supply, using transistors with higher  $V_t$  and shutting down the power completely (power gating) from unused parts of the chip. Typical methods for controlling the dynamic power consumption are clock gating, operand isolation and dynamic voltage and frequency scaling (DVFS). The first two are supported by electronics design automation (EDA) tools when using RTL design methodology, while the latter usually required manual implementation. So far, no DVFS has been deployed in hybrid pixel readout chips.

Minimizing the switching capacitance by avoiding long metal wires that

constantly change their value also reduces the dynamic power consumption. The architectural choices also have a large impact on the dynamic power consumption. A simple example of this is a reduction of a 64-bit bus to a 16-bit bus and sending four words in one transaction of four clock cycles instead of one transaction of one clock cycle. This effectively reduces the instantaneous power consumption by four (on average) but decreases throughput of the bus. Note that this method does not save any energy.

In applications requiring low duty cycles, power gating (also known as power pulsing or power cycling) can also be used to reduce the power consumption. In this scheme, electronics are switched into a lower power state by either switching off the power supply or by altering the bias voltages of transistors to reduce their current consumption. The former option is especially useful for digital logic in which no state information needs to be saved. The latter option is more suitable for analog electronics because it does not increase additional transistors and thus additional noise to power supply lines.

#### 1.2.4 Other types of pixel detectors

In addition to HPDs, there are other types of pixel detectors. Passive detectors like charge-coupled devices (CCDs) contain no active electronics and are not discussed in this thesis. Like HPDs, they use solid-state sensors for collecting the charge.

Another type of active detectors besides HPDs is the monolithic active pixel sensor (MAPS). Unlike HPDs, they consist of a single chip only, where it functions as a sensor and a readout chip at the same time. A cross-section of a MAPS detector is shown in Figure 1.6. The charge is collected by the n-well diode. The sensor is only fully depleted under this diode, and the charge collection is incomplete elsewhere in the epitaxial layer [12]. In addition to charge collection, they contain signal processing functionality, typically an amplification and digitization of signals. MAPSs cannot be implemented using standard CMOS processes, and require additional processing steps, for example triple wells, if CMOS logic is used.

Integrating the sensor and the readout electronics into the same ASIC is an advantage in terms of cost compared to HPDs. In MAPS, pixels can be implemented with as few as three transistors per pixel and the pixel pitch can be smaller than 10  $\mu$ m but have smaller signal-to-noise ratio (SNR) than HPDs [27]. The noise is produced by a phenomenon called dark current [28].

A typical digital camera found in cell phones is usually implemented as a MAPS because it requires smaller pixels, has to be cheap to manufacture and requires only frame readout rates of the order of few kHz. The readout rates of MAPSs are in general limited by the CMOS technology and the relative simplicity of the circuitry inside a pixel. Layout techniques like

Figure 1.6: A cross-section of an MAPS showing the n+-well diode on the p-epitaxial layer. [12]

triple-well can be used in MAPS to have the benefits of full-fledged static CMOS design at the expense of extra process layers and the extra area taken by the triple-well.

MAPSs are also less resilient to radiation effects than HPDs. This is an important attribute, particularly for high-energy physics experiments, where total dose of radiation can be hundreds of Mrads or even higher [29]. HPDs on the other hand are more expensive to manufacture than MAPSs because they require additional processing steps for connecting the sensor to the readout chip. Despite this cost, they have been deployed in applications where the requirements of readout speed and radiation tolerance cannot be met by MAPS.

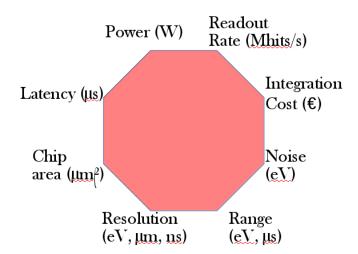

### 1.3 Requirements

Figure 1.7 shows a set of performance metrics that need to be chosen for each readout architecture designed for tracking applications. Each parameter is shown with its typical unit. Generally, when performance in one category is improved, the expected performance in some other category deteriorates. For example, when the spatial resolution is improved (pixel size decreased), all other things being equal, power density and thus power consumption increases because power does not scale down with the pixel size. There are other metrics such as radiation hardness which typically have an impact on power consumption, chip area and indirectly to other metrics as well. The most relevant metrics for this thesis are readout rate, power, chip area, timing range and timing resolution. These will be discussed in more detail

Figure 1.7: Different performance metrics for a pixel readout ASIC.

Table 1.1: General requirements for digital readout architectures.

| Pixel size       | $55 \ \mu m \times 55 \ \mu m$ |

|------------------|--------------------------------|

| Number of pixels | $256 \times 256$               |

| Chip area        | $2 \text{ cm}^2$               |

| Time resolution  | at least 25 ns                 |

| Timing range     | at least 9 bits                |

| Latency          | < Timing range                 |

| Power            | $< 1.5 \; { m W/cm^2}$         |

| Readout rate     | $> 40 \text{ Mhits/s/cm}^2$    |

particularly in Chapters 2 and 4.

Table 1.1 shows the general requirements for digital readout architectures presented in this thesis. The pixel and the matrix sizes are fixed to specific sizes but all the results presented later in this thesis are directly applicable to larger pixels sizes and smaller matrix sizes. Also, where mentioned, the results can be scaled to larger matrices as well. Time resolution must be always at least 25 ns with a range extending to at least 9 bits. Notice that the maximum latency here is simply the timing range. A detailed explanation of this will be given in Chapter 2. Due to limited cooling options in the hybrid pixel detectors, power consumption should be < 1.5 W/cm<sup>2</sup>. Finally, to improve readout rates compared to existing architectures, a minimum rate of 40 Mhits/s/cm<sup>2</sup> is required. As will be seen in Chapter 6, a factor of 10 higher rates than this can be achieved.

## 1.4 Scope and original contributions

This thesis focuses on the study and optimization of readout ASICs of HPDs in tracking applications. The scope of the work is digital very large scale integrated (VLSI) design, simulation and implementation. It studies digital data transfer techniques and their optimization from the pixel matrix to the periphery. It also studies on-chip data reduction techniques to overcome the problems of limited output bandwidth. Three original contributions to knowledge of the architectural design of HPD readout ASICs are presented:

- 1. The first contribution is a study to compare performance and implementation issues of several readout architectures, existing and new ones. The conceptual ideas from this study have then been tested by the author using high-level methodologies and simulation methods such as TLM and C++ simulation models. A subset of these simulations have then been performed at RTL. The physical implementation details of these architectures such as area and power are then studied in detail to estimate the feasibility of using these architectural techniques on a readout ASIC.

- 2. The second original contribution of this thesis is a sparse readout architecture capable of measuring time of arrival and charge of particles using a pixel of 55  $\mu$ m  $\times$  55  $\mu$ m for a mixed-signal chip called Timepix3 using 130 nm CMOS technology. In this chip, analog and digital elements are distributed uniformly across a chip of 1.4 cm  $\times$  1.4 cm, analog occupying 30 % and digital logic 70 % of the area. The author has designed and implemented the digital logic of the pixel and the super pixel. This includes all logic, buses and signal distribution required to transport data from the pixel matrix to the periphery as well as clock and time stamp distribution in the column. For the synchronizer in the digital front-end, the author has taken an existing design and adapted it to fit into new application. The author has also designed End of Column (EoC) block and periphery data bus architecture and arbitration for this chip. This chip has successfully been manufactured in silicon and its performance assessed. A comparison has been made between the simulated performance and the measurements.

- 3. The third contribution is the conceptual design, analysis and implementation of an architecture at the post-layout level for an HPD readout chip called VeloPix using 130 nm CMOS process. The author has designed a novel architecture for transporting data from the pixel matrix into the periphery. The periphery has also been designed to

sustain rates of over 1 Ghits/s/chip. The major challenges in addition to limited area available are the unprecedented data rates for HPD readout ASICs and the requirement of SEE tolerance which has been addressed using TMR techniques. This solution is capable of delivering more than 850 Mhits/s/ $cm^2$  from a pixel matrix, or 320 Mpackets/s/ $cm^2$  where each packet can contain 23 bits of information. This chip also features a novel solution for equalizing hit traffic from columns before they are sent off the chip.

Contributions presented here are based on RTL digital design principles to make them transferable to newer CMOS technologies more easily than custom circuit implementations. This implies reduced design time and cost while offering digital simulation and timing analysis tools for the verification of the designs. Higher level techniques such as TLM and behavioral (non-synthesizable) modelling have also been used in the architectural studies to allow exploration of larger range of design parameters in shorter time.

Timepix3 has been designed between 2010-2013, the chip being submitted in 24th May 2013. The first 6 wafers were received at the end of August 2013. Apart from the author's contribution, several designers from CERN (Geneva, Switzerland), Nikhef (Amsterdam, Netherlands) and the University of Bonn (Bonn, Germany) have contributed to the implementation and ideas of the chip. The design of VeloPix started in 2013 after the submission of Timepix3. It is a joint effort between CERN and Nikhef to design a new hybrid pixel readout chip for the upgrade of VELO of the LHCb experiment at CERN.

The work discussed and presented in this thesis in based on and extended from the publications listed below:

- T. Poikela, J. Plosila, T. Westerlund, M. Campbell, M. De Gaspari, X. Llopart, V. Gromov, R. Kluit, M. van Beuzekom, F. Zappon, V. Zivkovic, C. Brezina, K. Desch, Y. Fu, and A. Kruth. Timepix3: a 65K channel hybrid pixel readout chip with simultaneous ToA/ToT and sparse readout. Journal of Instrumentation, 9(05):C05013, 2014.

[30]

- T. Poikela, J. Plosila, T. Westerlund, J. Buytaert, M. Campbell, M. De Gaspari, X. Llopart, K. Wyllie, V. Gromov, R. Kluit, M. van Beuzekom, F. Zappon, V. Zivkovic, C. Brezina, K. Desch, Y. Fu, and A. Kruth. Digital column readout architectures for hybrid pixel detector readout chips. Journal of Instrumentation, 9(01):C01007, 2014.

[31]

- 3. T. Poikela, J. Plosila, T. Westerlund, J. Buytaert, M. Campbell, X. Llopart, R. Plackett, K. Wyllie, M. van Beuzekom, V. Gromov, R.

- Kluit, F. Zappon, V. Zivkovic, C. Brezina, K. Desch, X. Fang, and A. Kruth. Architectural modeling of pixel readout chips Velopix and Timepix3. Journal of Instrumentation, 7(01):C01093, 2012. [32]

- 4. M. van Beuzekom, J. Buytaert, M. Campbell, P. Collins, V. Gromov, R. Kluit, X. Llopart, T. Poikela, K. Wyllie, and V. Zivkovic. Velopix ASIC development for LHCb VELO upgrade. Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, (0):0, 2013. [33]

- V. Gromov, M. van Beuzekom, X. Fang, A. Kruth, R. Kluit, F. Zappon, V. Zivkovic, M. Campbell, T. Poikela, X. Llopart, C. Brezina, and K. Desch. Development and Applications of the Timepix3 Readout Chip. page 046. 20th Anniversary International Workshop on Vertex Detectors, Rust(Austria), June 2011 [34]

- 6. M. De. Gaspari, J. Alozy, R. Ballabriga, M. Campbell, E. Frojdh, J. Idarraga, S. Kulis, X. Llopart, T. Poikela, P. Valerio, and W. Wong. Design of the analog front-end for the Timepix3 and Smallpix hybrid pixel detectors in 130 nm CMOS technology. Journal of Instrumentation, 9(01):C01037, 2014. [16]

- P. Valerio, J. Alozy, S. Arfaoui, R. Ballabriga, M. Benoit, S. Bonacini, M. Campbell, D. Dannheim, M. De Gaspari, D. Felici, S. Kulis, X. Llopart, A. Nascetti, T. Poikela, and W. S. Wong. A prototype hybrid pixel detector ASIC for the CLIC experiment. Journal of Instrumentation, 9(01):C01012, 2014. [35]

## 1.5 Related work and background

This section briefly summarizes the previous work done in the architectures of HPD readout ASICs, and offers a short motivation why this study is relevant. The technical details of these works are discussed in the following chapters of this thesis where applicable.

#### 1.5.1 Simulation studies

No extensive study and simulation of the HPD readout architectures has been published linking the architectural studies to physical VLSI circuit implementation details. Individual studies are usually targeted for a specific application only [36, 37, 38]. These studies do not include comparisons between different architectures. In [39], an architecture optimized for a specific occupancy and hit distribution is presented.

Some studies offer tools for the evaluation of different architectures, but do not study the actual architectures or link the physical implementation details to them [40, 41].

#### 1.5.2 Pixel readout architectures

In [12], an overview of mostly triggered readout architectures for hybrid pixel detectors is given. This serves as a good starting point for this study, and these architectures can be modified to operate continuously without a trigger signal.

Spatial resolution, which is directly related to the pixel pitch p, is an important parameter in pixel applications but not the only property of interest. In the architectures presented in this thesis, micrometer-level spatial resolution is combined with temporal resolution of nanosecond-level. The last parameter is the number of pieces of information (the number of pixels hit) with a given spatial and temporal resolution that can be measured and transferred from the readout chip to the data analysis tools.

HPDs with the same or smaller pixel pitch of 55  $\mu$ m have already been manufactured [25, 42, 43, 44]. However, these chips are either lacking in time measurement capabilities [42, 43, 44], or cannot do simultaneous measurement of time and charge [25]. Chips with the simultaneous measurement capability have bigger pixel size, and thus lack in spatial resolution [37, 45, 46].

Some previous architectures are lacking in timing resolution and spatial resolution, typically having a minimum timing resolution of 25 ns[47, 48, 49].

Simultaneous time and charge measurement has been implemented with a pixel pitch of 25  $\mu$ m [35] in 65 nm CMOS. However, this chip is at the prototype stage spanning only 1.6 mm  $\times$  1.6 mm, and having short dynamic range for timing measurement (4 bits at maximum of 100 MHz) because it is targeted for one specific application.

None of the chips cited have a minimum timing resolution of 1.5625 ns, which is targeted by one of the architectures presented in this thesis, except [45] which has a timing resolution better than 100 ps, but it also has a pixel 30 times larger than in the architecture presented in this thesis. None of the readout chip architectures mentioned above can provide trigger-less, continuous information with a rate of 40 Mhits/s/cm² or higher while having the spatial and timing resolution mentioned above.

By doing this PhD study, some missing features of related works are addressed. However, it needs to be noted that the HPD readout ASICs are usually highly customized for a particular application and its requirements, so completely generic, "one-size-fits-all" solution is unlikely to be found for all pixel detectors. Even so, information and outcomes of this thesis will be useful for future studies and simulation of HPD readout ASICs. In the fol-

lowing chapters, the technical details of existing architectures are analyzed and new options are also given. The simulation methodology used in this thesis is also presented, and its advantages and disadvantages discussed. The thesis is concluded by a presentation of two readout chips and their architectures targeting specific applications. One of them has been manufactured in silicon and tested to be fully functional. The other architecture has been implemented at the layout-level but not manufactured yet.

## Chapter 2

# Hybrid pixel detector readout ASIC architectures

In this chapter, different concepts of readout architectures of HPD ASICs are described. First, architectural details of a generic chip are shown. Definitions are presented for several characteristics of HPD readout ASICs to allow comparison of different chip architectures. Analysis of different readout architectures using simulation is presented with the comparison of simulation results between the architectures. Simulations in this chapter have been performed using SystemC [50] and non-synthesizable high-level models (except where stated otherwise) to facilitate faster modelling and simulation than with RTL or gate-level techniques. TLM techniques [51] have been used to connect the models together. The author has carried all the modelling, simulation, verification and analysis work required for this chapter.

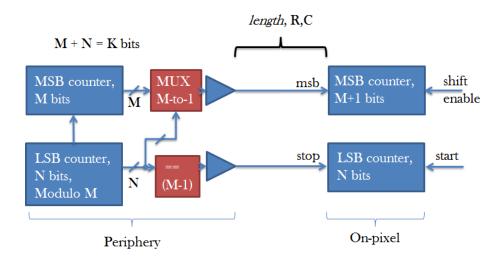

The novelties presented in this chapter are a time stamping method to reduce the routing overhead and switching activity caused by sending the time stamp up the pixel column, and two different pixel readout architectures. The first one consists of data nodes communication locally with each other and propagating the data down the column through registers in the nodes. The second one is an extension of the data nodes to a network in which data is sent either horizontally or vertically to a next node.

From the simulations and analysis design guidelines are drawn which will be used later in this thesis for the architectural design of specific HPD readout ASICs. At the end of the chapter, related work and existing HPD readout ASICs are briefly summarized based on the definitions laid out earlier in this chapter.

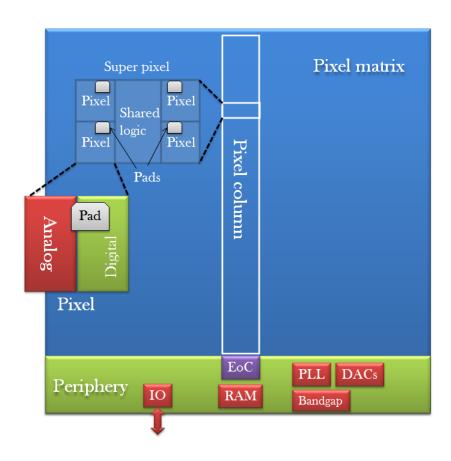

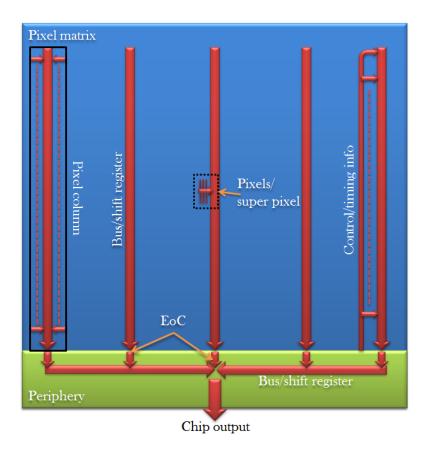

## 2.1 Architecture of hybrid pixel detector ASIC

Figure 2.1 shows a general architecture which can be tiled from three sides. This means that any  $2 \times N$  sensor ladder can be constructed from it. The advantage of the possibility to tile multiple chips together is to minimize dead area between sensors while being able to construct larger sensitive surfaces than from a single chip. Because yield of the sensor and readout chips is related to the total area per chip, the largest possible chip size may not always be desirable in terms of yield. On the other hand, there are other considerations such as unit cost per area where larger chips may be beneficial.

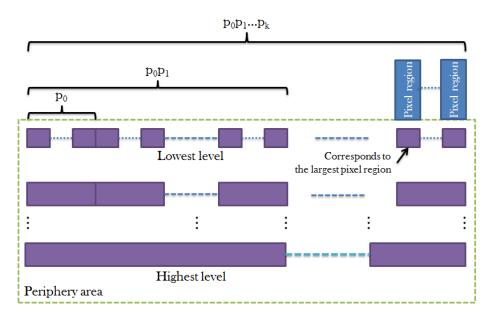

The chip is divided into two distinct parts, namely a pixel matrix and a periphery. As can be seen, most of the area is taken by the pixel matrix. Many HPD readout ASICs have this kind of division into a pixel matrix and a periphery [47, 48, 49, 25, 37, 45, 35]. The matrix is also called an active area because it corresponds to the sensitive part of the sensor. Ideally, the area taken by the periphery would be eliminated altogether to have the full chip covered by active area and to use it in four-side detector tiling. This would require usage of vertical buried interconnections called through-silicon vias (TSVs) [52], and would require having all input-output (IO) functionality on the backside of the readout chip. Ultimately TSVs enable 3D-integration of separate readout ASICs for analog and digital electronics.

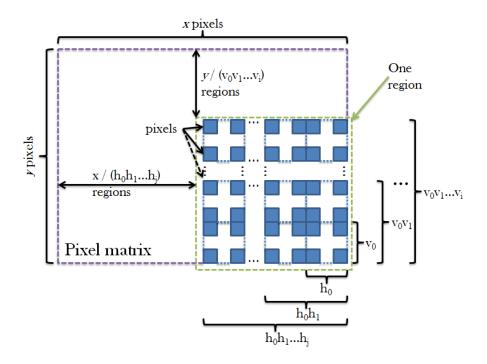

#### 2.1.1 Pixel matrix

A pixel matrix contains pixel unit cells (PUCs) connected to a sensor using bump-bonding techniques. A generic PUC is also described in [12]. Each PUC contains an analog signal processing electronics and in most cases digital logic for measurements and reading out the measurement data. This pulse processing chain is illustrated by Figure 2.2. The analog front-end is used for amplifying electrical signals arriving from sensors. These signals are typically short current pulses. It can also contain some pulse shaping functionality, threshold calibration, digital-to-analog converter (DAC) functionality and a digitisation scheme such as an analog-to-digital converter (ADC) or a discriminator. The pulse shaping is utilized to shape the signal suitable for ADCs or a discriminator. Local DACs are used to minimize the pixel-to-pixel threshold variations due to mismatches arising from process variations. Although most of these components are usually integrated inside a single pixel, for example in [45] there is no digital processing inside the pixel. Because HPD ASICs are very area-critical designs, front-ends and sensor signal processing cannot always be fully decoupled from the readout logic. One important concept related to the analog front-end is pile-up, which means the accumulation of charge into the electronics. Every time a

Figure 2.1: Structure of an HPD readout chip.

Figure 2.2: Pulse processing chain in an HPD readout chip.

signal arrives from a sensor, it carries a certain amount of charge. If the rate of the arrival of signals is high enough, the charge from the previous signal cannot be discharged completely. This leads to loss of charge information, and in the case of high rate, to a loss of all hit information.

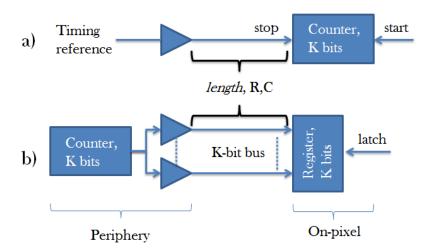

The digital front-end typically contains synchronization logic, time-to-digital converters (TDCs), counters for measurements and memories for data storage and buffering. One essential function in chips utilizing a clock signal is to synchronize asynchronous hit events to the measurement clock to avoid glitches in counters that can cause errors in timing measurements. Upsets can arise if a gated clock signal has a glitch which is seen by some counter flip-flops but not all of them. The same situation occurs if an asynchronous hit signal is directly used as a counter enable signal, and is seen by only some flip-flops. Both cases lead to corruption of counter values and to incorrect measurement.

The digital front-end can also contain some intermediate buffering stages but the number of buffer slots is usually restricted by the area. While buffering can reduce the inefficiencies from high activity events, it also adds latency to the events before they are transmitted. Pile-up or hit overflow can also occur in digital electronics, if the digital front-end cannot store hit information from an event. This pile-up usually occurs due to dead-time in reading out the information from the pixel.

Several digital front-ends can share a common structure which is called a pixel region or a super pixel. These terms can be used interchangeably, and only the super pixel is used in this thesis. This grouping is also illustrated in Figure 2.1. A super pixel typically contains a common data buffer or memory, arbitration logic and some logic to interface with a column bus. In the case of a shift-register based column design, a super pixel can contain extra logic for zero suppression such as a hit-flag register [35]. If automated place and route (PnR) tools are used for laying out the super pixel, each digital front-end may have a different physical layout. This "flattening" of the design improves utilization and logic optimization between blocks but may cause mismatches in timing and differences in crosstalk between the digital and analog front-ends of the super pixel. These differences in crosstalk then manifest as variations in noise of analog front-ends.