# Fabrication and Pseudo-Analog Characteristics of ${\rm Ta_2O_5\text{-}Based}$ Reram Cell

#### Mika Grönroos

2016

Master's thesis

University of Turku

Department of Information Technology

Supervisors:

Prof. Takahashi Yasuo

Prof. Arita Masashi

Ph.D. LEHTONEN Eero

Examiners:

D.Sc. Laiho Mika

Ph.D. Punkkinen Risto

#### TURUN YLIOPISTO

Informatioteknologian laitos

MIKA GRÖNROOS  ${\rm Ta}_2{\rm O}_5\text{-perustuvan ReRAM-muistisolun valmistus ja pseudoanaloginen toiminta}$

Diplomityö, 99 sivua Mikroelektroniikka Heinäkuu 2016

Memristori on yksi elektroniikan peruskomponenteista vastuksen, kondensaattorin ja kelan lisäksi. Se on passiivinen komponentti, jonka teorian kehitti Leon Chua vuonna 1971. Kesti kuitenkin yli kolmekymmentä vuotta ennen kuin teoria pystyttiin yhdistämään kokeellisiin tuloksiin. Vuonna 2008 Hewlett Packard julkaisi artikkelin, jossa he väittivät valmistaneensa ensimmäisen toimivan memristorin.

Memristori eli muistivastus on resistiivinen komponentti, jonka vastusarvoa pystytään muuttamaan. Nimensä mukaisesti memristori kykenee myös säilyttämään vastusarvonsa ilman jatkuvaa virtaa ja jännitettä. Tyypillisesti memristorilla on vähintään kaksi vastusarvoa, joista kumpikin pystytään valitsemaan syöttämällä komponentille jännitettä tai virtaa. Tämän vuoksi memristoreita kutsutaankin usein resistiivisiksi kytkimiksi.

Resistiivisiä kytkimiä tutkitaan nykyään paljon erityisesti niiden mahdollistaman muistiteknologian takia. Resistiivisistä kytkimistä rakennettua muistia kutsutaan ReRAM-muistiksi (lyhenne sanoista resistive random access memory). ReRAM-muisti on Flash-muistin tapaan haihtumaton muisti, jota voidaan sähköisesti ohjelmoida tai tyhjentää. Flash-muistia käytetään tällä hetkellä esimerkiksi muistitikuissa. ReRAM-muisti mahdollistaa kuitenkin nopeamman ja vähävirtaiseman toiminnan Flashiin verrattuna, joten se on tulevaisuudessa varteenotettava kilpailija markkinoilla.

ReRAM-muisti mahdollistaa myös useammin bitin tallentamisen yhteen muistisoluun binäärisen ("0" tai "1") toiminnan sijaan. Tyypillisesti ReRAM-muistisolulla on kaksi rajoittavaa vastusarvoa, mutta näiden kahden tilan välille pystytään mahdollisesti ohjelmoimaan useampia tiloja. Muistisoluja voidaan kutsua analogisiksi, jos tilojen määrää ei ole rajoitettu. Analogisilla muistisoluilla olisi mahdollista rakentaa tehokkaasti esimerkiksi neuroverkkoja. Neuroverkoilla pyritään mallintamaan aivojen toimintaa ja suorittamaan tehtäviä, jotka ovat tyypillisesti vaikeita perinteisille tietokoneohjelmille. Neuroverkkoja käytetään esimerkiksi puheentunnistuksessa tai tekoälytoteutuksissa.

Tässä diplomityössä tarkastellaan  ${\rm Ta_2O_5}$ -perustuvan ReRAM-muistisolun analogista toimintaa pitäen mielessä soveltuvuus neuroverkkoihin. ReRAM-muistisolun valmistus ja mittaustulokset käydään läpi. Muistisolun toiminta on harvoin täysin analogista, koska kahden rajoittavan vastusarvon välillä on usein rajattu määrä tiloja. Tämän vuoksi toimintaa kutsutaan pseudoanalogiseksi. Mittaustulokset osoittavat, että yksittäinen ReRAM-muistisolu kykenee binääriseen toimintaan hyvin. Joiltain osin yksittäinen solu kykenee tallentamaan useampia tiloja, mutta vastusarvoissa on peräkkäisten ohjelmointisyklien välillä suurta vaihtelevuutta, joka hankaloittaa tulkintaa. Valmistettu ReRAM-muistisolu ei sellaisenaan kykene toimimaan pseudoanalogisena muistina, vaan se vaati rinnalleen virtaa rajoittavan komponentin. Myös valmistusprosessin kehittäminen vähentäisi yksittäisen solun toiminnassa esiintyvää varianssia, jolloin sen toiminta muistuttaisi enemmän pseudoanalogista muistia.

Avainsanat: memristori, ReRAM, analoginen muisti, neuroverkot

#### UNIVERSITY OF TURKU

Department of Information Technology

MIKA GRÖNROOS Fabrication and Pseudo-Analog Characteristics of Ta<sub>2</sub>O<sub>5</sub>-Based ReRAM Cell

Master's thesis, 99 pages Microelectronics July 2016

The memristor is one of the fundamental circuit elements in addition to a resistor, capacitor and an inductor. It is a passive component whose theory was postulated by Leon Chua in 1971. It took over 30 years before any known physical examples were discovered. In 2008 Hewlett Packard published an article where they manufactured a device which they claimed to be the first memristor found.

The memristor, which is a concatenation of memory resistor, is a resistive component that has an ability to change its resistance. It can also remember its resistance value without continuous current or voltage. Typically, a memristor has at least two resistance states that can be altered. This is the reason why memristors are also called resistive switches.

Resistive switches can be used in memory technologies. A memory array that has been built using resistive switches is called ReRAM (resistive random access memory). ReRAM, like Flash memory, is a non-volatile memory that can be programmed or erased electrically. Flash memories are currently used e.g. in memory sticks. However, compared to Flash, ReRAM has faster operating speed and lower power consumption, for instance. It could potentially replace current memory standards in future.

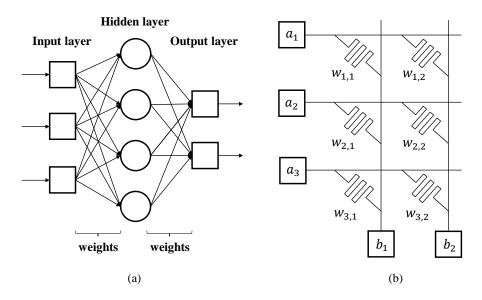

A ReRAM memory cell can also store multiple bits instead of binary operation ("0" or "1"). Typically there exists multiple intermediate resistance states between ReRAM's limiting resistances that could be utilized. Such memory could be called analog, if the amount of intermediate states is not limited to discrete levels. Analog memories make it possible to build artificial neural networks (ANN) efficiently, for instance. ANNs try to model the behaviour of brain and to perform tasks that are difficult for traditional computer programs such as speech recognition or artificial intelligence.

This thesis studies the analog behaviour of Ta<sub>2</sub>O<sub>5</sub>-based ReRAM cell. Manufacturing process and measurement results are presented. The operation of ReRAM cell is rarely fully analog as there exists limited amount of intermediate resistance states. This is the reason why operation is called pseudo-analog. Measurement results show that a single ReRAM cell is suitable for binary operation. In some cases, a single cell can store multiple resistance values but there exists significant variance in resistance states between subsequent programming cycles. The proposed ReRAM cell cannot operate as pseudo-analog ReRAM cell in itself as it needs an external current limiting component. Improving the manufacturing process should reduce the variability such that the operation would be more like a pseudo-analog memory.

Keywords: memristor, ReRAM, analog memory operation, artificial neural network

トゥルク大学 大学院情報科学研究科

MIKA GRÖNROOS: Ta<sub>2</sub>O<sub>5</sub>抵抗変化型メモリの作製とアナログメモリ動作

修士論文, 99 頁 マイクロエレクトロニクス 2016 年 7 月

メモリスタは、抵抗、容量、インダクタの3回路要素に加えて、もう一つの回路要素として話題になった、Leon Chuaが1971年に提案した受動素子である。30年以上もこの素子は見つけられていなかったが、2008年にHewlett Packard社が、最初のメモリスタ素子を発見したという論文を出した。

メモリスタはメモリとレジスタを合体したような語であるが、その抵抗が可変な素子である。また、その抵抗は、単調な電圧と電流の関係で示されない特徴がある。典型的なメモリスタ素子は、少なくとも2つの抵抗値を取り、その間で変化するので、レジスティブスイッチ(抵抗スイッチ)とも呼ばれている。

レジスティブスイッチは、メモリとして利用で、アレイ状に配置したものは、ReRAM (resistive random access memory)と呼ばれている。ReRAMは、メモリスティックなどに使われているFlashメモリと同様の機能を持ち、不揮発性(電源のサポート無しにメモリ状態を保持できる)で、電気的に書き換えが可能である。加えて、ReRAMは、Flashと比べて、高速動作と低消費電力の特徴を併せ持つ。したがって、将来のメモリスタンダードを書き換える可能性を秘めている。

ReRAMセルは、従来の2値のバイナリ情報("0" or "1")だけではなく、多値の情報を記憶することも可能である。すなわち、ReRAMの持つ抵抗制限の範囲で、いくつかの中間的な抵抗値を取ることができ、この中間的抵抗値が連続に選択可能になれば、アナログメモリと呼ぶことが可能となる。このようなアナログメモリは、効果的な人工ニューラルネットワークを構成することを可能にする。人工ニューラルネットワークは、人間の脳のように、従来のコンピュータが苦手とする言葉や顔の認識などを可能にする。

本論文は、Ta<sub>2</sub>O<sub>5</sub> を用いたReRAMのアナログ特性について研究したものであり、その作製方法と評価結果を示してある。ReRAMの動作は、フルにアナログにはならずに、限られた中間状態を取る准アナログと呼ばれる状況にある。実際の測定結果は、ReRAMがバイナリ動作に向いていることを示した。いくつかの場合、1個のReRAMセルが多値を取る結果が得られているが、連続する繰返しの中でも、抵抗値がばらつく現象が見られる。試作したReRAMセルは、准アナログ素子としては動作しなかったが、電流制限素子の付加で改善できる可能性がある。更なる作製プロセスの改善で抵抗ばらつきを減らすことで、准アナログ的な動作が可能になると考えられる。

# Table of Contents

| Lı | ST OF                                          | F Symbols and Acronyms                             | iii |  |  |  |

|----|------------------------------------------------|----------------------------------------------------|-----|--|--|--|

| 1  | Introduction                                   |                                                    |     |  |  |  |

|    | 1.1                                            | Motivation and Approach                            | 3   |  |  |  |

|    | 1.2                                            | Organization of Thesis                             | 4   |  |  |  |

| 2  | Fun                                            | IDAMENTAL CIRCUIT ELEMENTS                         | 6   |  |  |  |

|    | 2.1                                            | Four Basic Circuit Variables                       | 6   |  |  |  |

|    | 2.2                                            | Three Basic Circuit Elements                       | 7   |  |  |  |

|    | 2.3                                            | 3 The Fourth Element – Memristor                   |     |  |  |  |

|    | 2.4                                            | Pinched Hysteresis of Memristor                    | 12  |  |  |  |

| 3  | Physical Realization of Memristor 16           |                                                    |     |  |  |  |

|    | 3.1                                            | HP's Device Model and Physical Properties          |     |  |  |  |

|    | 3.2                                            | Resistive Switching                                |     |  |  |  |

|    | 3.3                                            | Filamentary and Interface Type Switching Models    | 24  |  |  |  |

|    |                                                | 3.3.1 Filamentary Type Model                       | 24  |  |  |  |

|    |                                                | 3.3.2 Interface Type Model                         | 27  |  |  |  |

|    | 3.4                                            | Redox-Based Switching Mechanisms                   | 28  |  |  |  |

|    |                                                | 3.4.1 Electrochemical Metallization Effect         | 28  |  |  |  |

|    |                                                | 3.4.2 Valence Change Memory Effect                 | 29  |  |  |  |

|    |                                                | 3.4.3 Thermochemical Memory Effect                 | 29  |  |  |  |

| 4  | Applications of Resistive Switching Devices 32 |                                                    |     |  |  |  |

|    | 4.1                                            | Digital Applications                               | 34  |  |  |  |

|    | 4.2                                            | Analog Applications                                | 35  |  |  |  |

|    | 4.3                                            | Resistive Random Access Memory                     | 37  |  |  |  |

|    | 4.4                                            | A Brief Introduction to Artificial Neural Networks | 41  |  |  |  |

| 5  | FABRICATION OF $Ta/Ta_2O_5/TiN$ RERAM DEVICES 43                                        |                                                                                   |                                                  |    |  |  |  |

|----|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------|----|--|--|--|

|    | 5.1                                                                                     | Organic and Inorganic Cleaning                                                    |                                                  |    |  |  |  |

|    | 5.2                                                                                     | Deposition of Bottom Electrode and Insulation Layer with Sputtering 46            |                                                  |    |  |  |  |

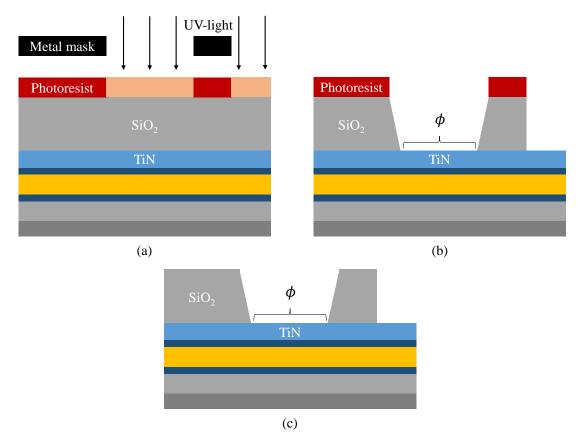

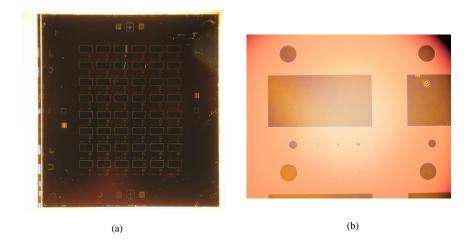

|    | 5.3                                                                                     | First Photoresist Application and Photolithography                                |                                                  |    |  |  |  |

|    | 5.4                                                                                     | Reactive Ion Etching and O <sub>2</sub> Plasma Ashing without Tunnel              |                                                  |    |  |  |  |

|    | 5.5                                                                                     | Second Photoresist Application, Photolithography and O <sub>2</sub> Plasma Ashing |                                                  |    |  |  |  |

|    |                                                                                         | with Tunnel                                                                       |                                                  |    |  |  |  |

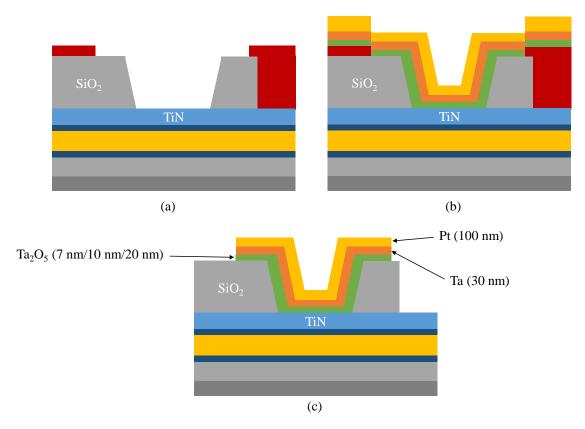

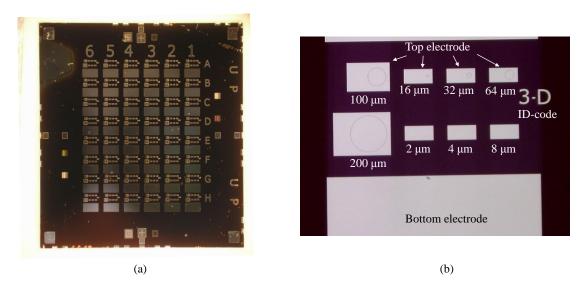

|    | 5.6                                                                                     | Deposition of Top Electrode with Sputtering and Lift-Off                          |                                                  |    |  |  |  |

| 6  | MEASUREMENTS AND CHARACTERISTICS OF Ta/Ta <sub>2</sub> O <sub>5</sub> /TiN RERAM CELL 5 |                                                                                   |                                                  |    |  |  |  |

|    | 6.1                                                                                     | Gener                                                                             | al Characteristics                               | 54 |  |  |  |

|    |                                                                                         | 6.1.1                                                                             | Initial Forming Voltage and Resistance           | 56 |  |  |  |

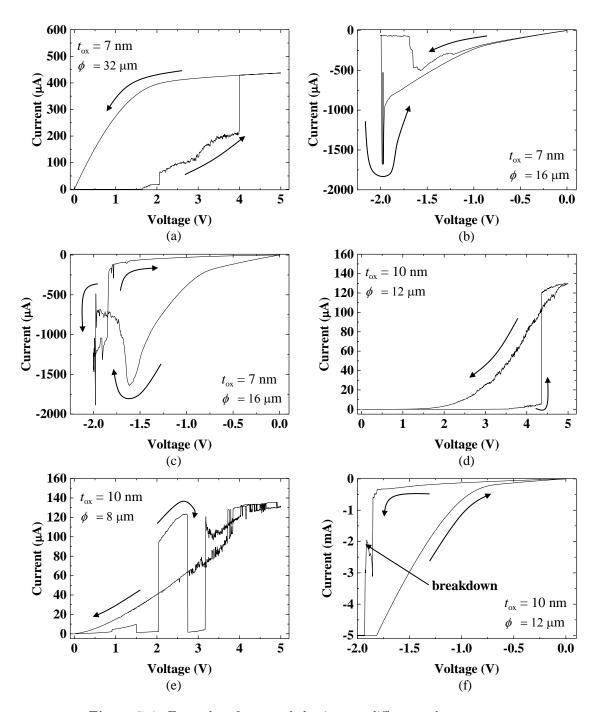

|    |                                                                                         | 6.1.2                                                                             | Typical Current-Voltage Characteristics          | 58 |  |  |  |

|    |                                                                                         | 6.1.3                                                                             | Understanding the Breakdown Mechanisms           | 60 |  |  |  |

|    |                                                                                         | 6.1.4                                                                             | Relationship Between Forming and Reset Processes | 62 |  |  |  |

|    |                                                                                         | 6.1.5                                                                             | Retention                                        | 64 |  |  |  |

|    |                                                                                         | 6.1.6                                                                             | Endurance and $R_{\rm OFF}/R_{\rm ON}$           | 64 |  |  |  |

|    |                                                                                         | 6.1.7                                                                             | Pulse Measurements                               | 67 |  |  |  |

|    | 6.2                                                                                     | Physic                                                                            | cal Mechanisms Behind Switching                  | 68 |  |  |  |

|    | 6.3                                                                                     | Analog Behaviour                                                                  |                                                  |    |  |  |  |

| 7  | Cuf                                                                                     | CURRENT LIMITATION USING MOSFET 7                                                 |                                                  |    |  |  |  |

|    | 7.1                                                                                     | Fabrication of ${\rm Ta_2O_5}\text{-Based}$ Device with MOSFET                    |                                                  |    |  |  |  |

|    | 7.2                                                                                     | Measu                                                                             | arement and Characteristics                      | 81 |  |  |  |

| 8  | Con                                                                                     | ONCLUSIONS                                                                        |                                                  |    |  |  |  |

| Ві | Bibliography                                                                            |                                                                                   |                                                  |    |  |  |  |

# LIST OF SYMBOLS AND ACRONYMS

The following lists the symbols and the acronyms used in this thesis. If some symbol or acronym has other meaning or is missing from this listing, its definition should become clear from the context.

- $\rightarrow$  Material implication operation in Boolean algebra

- ∧ Logical AND operation in Boolean algebra

- ∨ Logical OR operation in Boolean algebra

- ¬ Logical NOT operation in Boolean algebra

- $a_i$  Input parameter of ANN

- $A_{\mathrm{mem}}$  Area of memory matrix

- $\alpha$  Shape parameter of parabel at Fermi level

- $b_j$  Output parameter of ANN

- B Subset  $\{0,1\}$  of real numbers

- B Magnitude of magnetic field

- C Capacitance

- e Elementary charge

- $e^-$  Electron

- E Electrical potential energy

- $E_b$  Bandgap energy

- $E_c$  Energy of conduction band

- $E_f$  Fermi energy

- $E_t$  Trap level energy

- $E_v$  Energy of valence band

- $\epsilon_0$  Vacuum permittivity

- $\epsilon_r$  Relative permittivity

- F Fabrication feature size

G Conductance

$G_0$  Quantized unit of electrical conductance

h Planck's constant

*i* Electric current

J Electric current density

L Inductance

M Memristance

$\mu$  Electron mobility

$\mu_V$  Average mobility of charge carriers

$n_0$  Concentration of free carriers in thermal equilibrium

Number of conducting filaments

$\omega_{\rm in}$  Angular input frequency

$\varphi, \varphi_B$  Magnetic flux or flux-linkage

$\phi$  Hole diameter of ReRAM cell

$\Phi$  Potential barrier height with respect to Fermi level

q Electric charge

R Resistance

$R_{\rm int}$  Intermediate resistance level

$R_{\text{OFF}}$  Off-resistance (or memristance)

$R_{\rm ON}$  On-resistance (or memristance)

$\mathbb{R}$  Set of real numbers

$\mathbb{R}^n$  *n*-dimensional set of real numbers

Surface of vector area

$\sigma$  Non-linear function in ANN

t Time

$t_{\rm ox}$  Oxide thickness of ReRAM cell

$\theta$  Ratio of the free carrier density to total carrier density

v Electrical voltage

$v_G$  MOSFET gate voltage

$v_D$  MOSFET drain voltage

$v_S$  MOSFET source voltage

W Memductance

$w_{i,j}$  Synaptic weight (or strength) in ANN

w Memristor's state variable

$\boldsymbol{w}$  *n*-dimensional state variable

$\dot{\boldsymbol{w}}$  *n*-state derivative of state variable

ALD Atomic layer deposition

ANN Artificial neural network

CAD Computer aided design

CBRAM Conductive bridge random access memory

CMOL A hybrid CMOS and resistive switch circuit

CMOS Complementary metal-oxide semiconductor

CMP Chemical mechanical planarization

CMR Colossal magnetoresistive (device)

CNN Cellular neural network

DC Direct current

DRAM Dynamic random access memory

ECM Electrochemical metallization effect

FPGA Field programmable gate array

HDD Hard disk drive

HMDS Hexamethyldisilazane

HRS High resistance state

ICP Inductively coupled plasma

LRS Low resistance state

MLC Multi-level cell

MOSFET Metal-oxide-semiconductor field-effect transistor

MRAM Magnetic random access memory

NVM Non-volatile memory

OxrRAM Transition metal-oxide resistive random access memory

PCM Phase change memory

PCRAM Phase change random acceess memory

PLD Pulse layer deposition

PMC Programmable metallization cell

PMGI Polymethylglutarimide QPC Quantum point contact RF Radio frequency

RIE Reactive ion etching

RRAM, ReRAM Resistive random access memory

SCLC Space charge limited conduction

SEM Scanning electron microscope

SRAM Static random access memory

STT-RAM Spin-torque transfer random access memory

STXM Scanning transmission x-ray microscope

TCM Thermochemical memory effect

TEM Transmission electron microscopy

VCM Valency change memory effect

WGFMU Waveform generator/fast measurement unit

# 1 Introduction

Fundamental physics behind electricity and magnetism are necessary to understand electronics and circuit theory. Discoveries such as resistance, capacitance and inductance serve as a basis for basic and complex circuit elements. Capacitor – an insulator between two conductors – was invented by German scientist Ewald Georg Von Kleist in 1745. Resistance and resistor were discovered in 1827 by Georg Ohm. Ohm deduced mathematical laws of resistance better known as Ohm's law which is one of the earliest concept in circuit theory. Soon after Ohm's findings, inductance, which is used in inductors and transformers was discovered separately in 1831 by two different scientists, Michael Faraday and Joseph Henry.

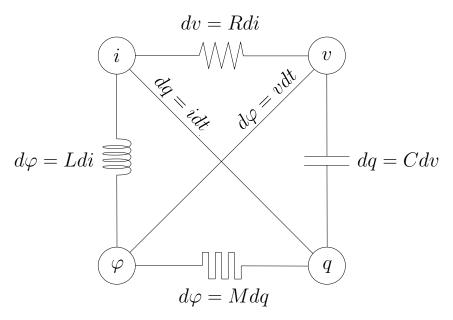

The three passive fundamental circuit elements: resistor, capacitor and inductor can be defined using four basic circuit variables: charge, current, voltage and magnetic flux. Passive elements do not need any external power supply to operate. Active circuit elements such as transistors make it possible to build complex circuits that are currently present everywhere around us but they are not called fundamental circuit elements. However, Leon Chua postulated existence of the fourth fundamental circuit element in 1971 [1], that would complete the symmetry of the four basic circuit variables.

Chua named his theoretical component as a *memristor* which is a concatenation of words memory resistor. As the name suggest, a memristor is similar to a non-linear resistor but the fundamental difference is that memristor can change and remember its resistance value even when no external voltage or current is applied to it. This kind of behaviour may be hard to understand intuitively. Also, the strange behaviour in voltage-current plane reveals a pinched hysteresis loop figure. There was no known physical examples of passive memristors for over 30 years after Chua's first publication but in 2008, Hewlett Packard successfully manufactured a device which they claimed to be the first memristor discovered [2]. Soon after their finding many other research groups reported memristor like behaviour in their experimental devices. It has to be noted that memristive

like behaviour was already observed in 1960s and Sharp and Samsung were conducting research on resistive switching memories in early 2000s. However, no one was able or did not try to apply memristive theory to experimental results. Currently memristor theory is a very active research field with many potential applications.

HP's memristor and also discoveries by other research groups are capacitor like thinfilm structures where a very thin layer of insulator material is manufactured between metal electrodes. The phenomena that triggers resistance change in materials is called *resistive* switching and many times these components are called *resistive switches* instead of memristors. Currently the exact physical mechanisms that occur inside resistive switches are not known. It is totally possible that there are multiple different mechanisms happening simultaneously which makes it hard to understand this phenomenon.

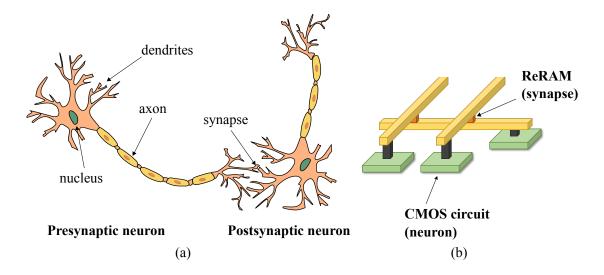

Naturally the memristor and resistive switches have an application field in memory technologies. Most of the research is towards resistive random access memory. Resistive random access memories have many different names in literature: ReRAM, RRAM or CBRAM but essentially they refer to the same thing. In this thesis the term ReRAM is used. Memory technologies can be divided into two categories; volatile memories need continuous power to store data and non-volatile memories can store their information for a long time after power is cut-off. ReRAM falls into a non-volatile memory category and it could replace current industry standard memory technologies like FLASH-memory that is commonly used e.g. in memory sticks. ReRAM could provide better energy efficiency, faster operating speed and longer retention time in smaller size, for instance [3]. There is also a possibility to store multiple bits in a single ReRAM cell instead of one bit ("0" or "1"). The possible application field of ReRAM is not only limited to memory technologies. There are attempts to use ReRAMs to perform similar computations than transistors perform in logic gates or to provide reconfigurability into analog integrated circuits. One interesting idea is to use ReRAMs for neuromorphic computing purposes like in artificial neural networks. Currently software implementations of artificial neural networks are used in image recognition, speech recognition or realizing artificial intelligence, for instance. ReRAMs could provide an efficient way to implement neural networks in hardware level.

Reliable operation is one of the big challenges in realizing resistive switching components. Materials and manufacturing process have an effect on resistive switching which is the reason why no single material combination is superior to any other. ReRAM's voltage-current behaviour as well as voltage impulse response should be analysed in order

to understand its performance suitability for proposed applications.

### 1.1 Motivation and Approach

The purpose of the research is to achieve pseudo-analog memory characteristics by the use of ReRAMs. Instead of digital operation, pseudo-analog operation allows continuous resistance levels to be utilized in memory. Functionality of such a device is not limited only to memory but it can be also used in computational purposes. The motivation is to realize a ReRAM cell whose resistance levels can be used as connection strength of synapses in artificial neural network systems. The electrical characteristics of one ReRAM cell should be reliable enough to make neural network like structure realistically achievable.

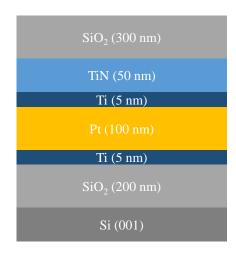

Tantalum pentoxide (Ta<sub>2</sub>O<sub>5</sub>) based ReRAM cell is proposed to achieve the necessary device requirements for analog memory. ReRAM cell's structure has tantalum top electrode, tantalum pentoxide insulating layer and titanium nitrate bottom electrode. The metal-insulator-metal test structures are fabricated on a silicon wafer with silicon dioxide layer by the use of RF sputtering, lithography and dry etching processes. Different oxide layer thicknesses as well as ReRAM cell areas are studied to see how they affect on ReRAM's electrical properties. The main method is to investigate voltage vs. current characteristics by the use of semiconductor parameter analyser. The measurement equipment provides limitation current that is necessary to prevent ReRAM's breakdown. Limitation current should be changed so that the ReRAM cell is able to achieve hysteresis memory characteristics.

In this study, the first step is to analyse the general characteristics of ReRAM cell. Understanding device's behaviour is crucial in order to realize analog operation. The method to achieve analog operation is to control negative reset voltage by modulating them with voltage sweeps. The next step is to investigate the resistance control by the voltage pulses considering the pulse-coupled neural network. Here the basic control factors are the pulse width and height. If the results are satisfactory, the following step is to control the resistance of ReRAM by the number of pulses, in which the control factor should be appropriately chosen.

Since the semiconductor parameter analyzer's limitation current was found to be insufficient for analog memory, a ReRAM cell with a MOSFET is examined. MOSFET provides another way to control the ReRAM's current by controlling the MOSFET's gate voltage. MOSFET is also proposed in literature to be a good selector in memory arrays that have a crossbar like structure. Artificial neural networks can be also implemented in crossbar arrays which is the reason that MOSFET-ReRAM structure and its electrical characteristics are studied in the same way as a single ReRAM cell.

## 1.2 Organization of Thesis

The structure of this thesis is the following:

In Chapter 2 the mathematical background as well as necessary terminology of memristor theory is given. The ideal voltage vs. current characteristics is presented. This chapter is mostly based on Chua's work [1,4].

Chapter 3 presents the physical processes that occur inside resistive switching. It begins with a short introduction of HP's memristor model and physical explanation. HP's device is chosen because their publication [2], was the first one that connected memristor theory with experimental results. The rest of the chapter presents the terminology and theory of filamentary and interfacial type resistive switching. The switching mechanisms known as redox-based effects that are observed in ReRAMs are also described.

A short introduction of different applications of resistive switching devices is presented in Chapter 4. Digital and analog applications are discussed. The main focus is on resistive random access memories and its comparison to other memory technologies. A very brief introduction to artificial neural networks and their realization using ReRAMs' is also given.

The Chapters 5, 6 and 7 are the practical part of this thesis. First, the manufacturing process is explained in sufficient detail. The general characteristics and measurement results are presented in Chapter 6. The important performance metrics are studied to understand how well the ReRAM cell can operate if analog operation is considered. There is also a brief section about the physical mechanisms that could be present in the ReRAM cell. Finally, the analog operation measurements are presented and analyzed. Chapter 7 describes the manufacturing process of MOSFET-ReRAM structure where measurement results before the final conclusions of this work are given.

In this thesis I manufactured and measured the proposed ReRAM cell. The aim of this thesis is to give a broad overview about memristive theory, physical processes behind resistive switching, ReRAM's practical applications and presenting experimental results of manufactured ReRAM cell. The theoretical background and physical switching

mechanisms are crucial to understand the electrical behaviour of the proposed ReRAM cell. The main scope of this thesis are the measurement results of  ${\rm Ta_2O_5}$ -based ReRAM cells and the analog memory characteristics. If the results are considered good enough for analog memory operation, this work could act as a base for further investigations of ReRAM based artificial neural networks.

# 2 Fundamental Circuit

# ELEMENTS

#### 2.1 Four Basic Circuit Variables

The elementary charge e is a fundamental physical constant that defines a charge that a single electron (or proton) carries. It is measured in coulombs (C) and its approximate value is

$$e = 1.6021766208 \cdot 10^{-19}$$

C (2.1)

according to NIST Reference on Constants, Units and Uncertainty. Elementary charge must not be confused with electric charge q. Electric charge is a quantity of charge carriers that flow through some cross section in time t

$$q = \int idt. (2.2)$$

The flow of charge carriers is called an electric current i and it is measured in amperes (A)

$$i = \frac{dq}{dt}. (2.3)$$

A quantity of one ampere is also defined by The International System of Units (SI) to be

"The constant current which, if maintained in two straight parallel conductors of infinite length, of negligible circular cross-section, and placed one meter apart in vacuum, would produce between these conductors a force equal to  $2 \cdot 10^{-7}$  newtons per metre of length."

but current of one ampere can be presented using another SI-unit called coulomb. In that

case, one ampere is one coulomb of charge going through a cross section in one second's time.

The electric voltage v is a difference of electric potential energy E between two points per unit electric charge. The electric voltage drives charge carriers between two points thus creating a current. In circuits voltage is measured in volts (V)

$$v = \frac{E}{q}. (2.4)$$

The fourth basic circuit variable is called magnetic flux (or flux linkage)  $\varphi$ . The magnetic flux is a time integral of electric voltage

$$\varphi = \int v dt \text{ or } v = \frac{d\varphi}{dt}$$

(2.5)

Now the four circuit variables  $\{i, q, v, \varphi\}$  have been defined and it can be seen that there exist six different pairwise relations between them

$$\{(v,i),(v,q),(i,\varphi),(\varphi,q),(v,\varphi),(i,q)\}.$$

(2.6)

#### 2.2Three Basic Circuit Elements

Out of six relations presented in (2.6) three of them are well known. The basic two-terminal passive circuit elements are resistor, capacitor and inductor whose circuit variable relations are (v,i), (v,q) and  $(i,\varphi)$  respectively. It's not necessary to present any equations of their physical behaviour here, but it is assumed that there exist implicit equations that define their properties. The following functions define the three fundamental circuit elements:

$$\int f_R(v,i) = 0 \tag{2.7}$$

$$\begin{cases} f_R(v,i) = 0 \\ f_C(v,q) = 0 \end{cases}$$

(2.7)

$$\int f_L(i,\varphi) = 0 \tag{2.9}$$

where R, C and L stand for resistance, capacitance and inductance respectively.

The previous three equations generalize non-linear fundamental circuit elements but they can be written as voltage or current derivatives of voltage, charge and flux:

$$\int dv = R(i)di \tag{2.10}$$

$$\begin{cases} dv = R(i)di & (2.10) \\ dq = C(v)dv & (2.11) \end{cases}$$

$$d\varphi = L(i)di \tag{2.12}$$

If the values of R(i), C(v) and L(i) are constant, the circuit elements are called *linear*. For example, a transistor is not a fundamental element because it is a three terminal externally driven component. On the other hand, a diode can be called a fundamental component because it is a non-linear version of resistor thus it belongs to the group of resistors. The unit values for resistance is  $ohm(\Omega)$ , for capacitance it is farad (F), and for inductance it is henry (H).

If (2.2) and (2.5) are written in the form where the current and voltage are integrated over infinite past, relations between inductors  $(i, \varphi)$  and capacitors (v, q) have the following expressions respectively

$$\varphi(t) = \int_{-\infty}^{t} v(\tau)d\tau = \varphi_0 + \int_{0}^{t} v(\tau)d\tau, \tag{2.13}$$

$$q(t) = \int_{-\infty}^{t} i(\tau)d\tau = q_0 + \int_{0}^{t} i(\tau)d\tau,$$

(2.14)

where  $\varphi_0$  and  $q_0$  are initial state of flux and charge at the initial time t=0. The two of these relations, namely those between  $(v,\varphi)$  and (i,q) are not constitutive relations because they are related with (2.13) and (2.14).

Out of six relations only one, namely  $(\varphi, q)$  has not been defined. In Chua's 1971 paper [1], he noticed this missing relation and postulated an existence of the memristor.

#### The Fourth Element – Memristor 2.3

Chua's memristor is a two-terminal passive device which is also known as flux-charge memristor. Memristor is the final constitutive relation thus completing the symmetry that is represented in Figure 2.1. The implicit function of memristor is defined in the same manner as in the case of other non-linear circuit elements

$$f_M(\varphi, q) = 0. (2.15)$$

**Figure 2.1:** Four fundamental circuit elements and their relations to circuit variables. Memristor symbol used in this thesis is shown in the bottom.

The charge derivative presentation is

$$d\varphi = M(q)dq \text{ or } M(q) = \frac{d\varphi}{dq}.$$

(2.16)

If (2.16) is substituted with dt, using (2.3) and (2.5) the following relation is obtained

$$M(q(t)) = \frac{d\varphi/dt}{dq/dt} = \frac{v(t)}{i(t)}$$

(2.17)

which can be written in the form

$$v(t) = M(q(t))i(t). (2.18)$$

Memristor has a function called *memristance*, M, it's unit value is ohm ( $\Omega$ ). The inverse of memristance is called *memductance*, W and it's unit value is siemens (S)

$$W(q(t)) = \frac{1}{M(q(t))} = \frac{i(t)}{v(t)}.$$

(2.19)

The previous equations are important to understand the  $q - \varphi$  and i - v properties of memristor. For example, if M is constant a memristor would be exactly the same as a linear resistor. However non-linear behaviour of M reveals some interesting properties. If (2.5) is used in (2.17) it is easy to see that memristor has a property of remembering

its resistance (memristor is a concatenation of *memory resistor*) which depends on the history of charge that has passed through it

$$v(t) = M\left(\int_{-\infty}^{t} i(\tau)d\tau\right)i(t). \tag{2.20}$$

Memristance keeps changing its value as long as input signal is applied to it. Removing input current (or voltage) makes memristor to keep its state indefinitely. Equation (2.20) defines a *current controlled* memristor.

It is important to understand that Chua's definition of memristor is a classification of *ideal* and *passive* component. Passivity means that component has no internal energy suppliers. Such component must satisfy the following properties in  $q - \varphi$  plane [1,5]:

Criteria 1:  $q - \varphi$  curve must be unique. Memristor behaves the same way regardless of input waveform. In the same initial condition  $(q_0, \varphi_0)$  memristor changes it's value always the same way if certain amount of charge (or flux) is applied to it.

Criteria 2:  $q - \varphi$  curve must be non-linear. Non-linearity ensures that memristor differentiates from resistor. If the  $q - \varphi$  curve is linear, memristance would be constant and memristor is indistinguishable from resistor. This does not contradict with previously claimed existence of four fundamental elements. A linear memristor belongs to the group of resistors but a non-linear (or linear) resistor does not belong to the group of non-linear memristors thus they are different fundamental elements.

Criteria 3:  $q - \varphi$  curve must be continuously differentiable and increasing. Continuously differentiable curve guarantees that memristance does not have any discontinuities and it's differentiable in every point thus M(q),  $\forall q$  has finite value. Increasing curve  $M(q) \geq 0$ ,  $\forall q$  ensures that ideal memristor will be passive. If the  $q - \varphi$  curve is not increasing there is some point  $q_a$ , where  $M(q_a) = \frac{d\varphi(q_a)}{dq} < 0$ , from which follows that voltage can have different polarity than current that is applied to component because instantaneous memristance  $M(q(t)) = \frac{v(t)}{i(t)} < 0 \Rightarrow v(t) < 0$  while i(t) > 0 (or vice versa). This contradicts with the passivity criteria because such component must have some internal power sources to keep the current flowing through same direction while the voltage over component is inverted. Also instantaneous power dissipated by passive memristor can not be negative,  $p(t) = v(t)i(t) = M(q(t))[i(t)]^2 \geq 0$  thus M(q) must be always positive. This criteria could be expanded to monotonically

increasing  $M(q) > 0, \forall q$  which limits the i-v curve to have exactly one point where  $v(t) = 0 \Leftrightarrow i(t) = 0$ . Such criteria could be called a *strict passivity* criteria.

Years later after Chua's first theorem of memristor it became clear that a single equation  $d\varphi = M(q)dq$  is not enough to explain its physical behaviour in the real world completely. Chua improved his theory on memristors with his former student Kang to generalize memristor to be a subset of memristive systems [4]. Memristive systems have input, output and most importantly a n-dimensional state variable  $\mathbf{w}$ . Memristor actually needs two equations to characterize it completely. The general equations of memristive systems are

$$y = g(\boldsymbol{w}, u, t)u \tag{2.21}$$

$$\dot{\boldsymbol{w}} = f(\boldsymbol{w}, u, t) \tag{2.22}$$

where functions f and g are continuous, g is the output signal, g is the input signal, g is time and g is g-state derivative of g. Chua noticed that some previously observed phenomena and devices would classify as memristive system. One example of such device is a component called g therefore whose resistance is dependent on its temperature. Another famous example is a circuit model of the North Atlantic squid's giant axon also known as g and g are g and g inventors Alan Lloyd Hodgkin and Andrew Huxley were awarded the Nobel Prize in physiology in 1965 and Chua proved that their model had a circuit equivalent where two memristors were used.

As mentioned previously, a passive memristor is a special case in memristive systems. Memristor's state depends on it's previous state and current or voltage input. Because there is no linear relation between current and voltage, memristor should have definition that is related to the physical realization of such device. General *n*th-order current controlled and voltage controlled memristors are represented by

$$v = R(\boldsymbol{w}, i, t)i \tag{2.23}$$

$$\dot{\boldsymbol{w}} = f(\boldsymbol{w}, i, t) \tag{2.24}$$

and

$$i = G(\boldsymbol{w}, v, t)v \tag{2.25}$$

$$\dot{\boldsymbol{w}} = f(\boldsymbol{w}, v, t) \tag{2.26}$$

Previous implicit equations do not describe behaviour of real physical devices. Most manufactured memristors are thin-film structures and their behaviour can not be categorized the same as flux-charge memristor. Chua mentioned in his memristive systems paper [4], that there are special cases where one-port device is time-invariant.

$$v = R(\boldsymbol{w})i \tag{2.27}$$

$$\dot{\boldsymbol{w}} = f(\boldsymbol{w}, i) \tag{2.28}$$

After HP's discovery in 2008 [2], it became more evident that the previous two equations were very useful in modelling their memristor's behaviour. The detailed equations are presented in Section 3.1 which include process and dimensional parameters. Physical models of two-terminal memristor typically have more limited state variable  $w \in \mathbb{R}$ .

Previously mentioned criteria and equations guarantee that memristor's i-v curve is a pinched hysteresis (Lissajous) curve with a zero crossing point. Chua proved mathematically that memristors can not be constructed using other passive fundamental components: resistors, capacitors and inductors.

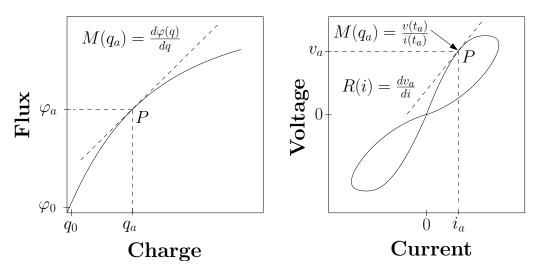

# 2.4 Pinched Hysteresis of Memristor

The relations between  $q - \varphi$  and i - v are easy to see with help of graphical representations. The continuous pinched hysteresis loop curve is also called the *fingerprint* of memristor. Hysteresis loop gives more intuitive information about memristor's behaviour while it is driven by a sinusoidal input signal. Based on the previously presented criteria memristor's i - v curve has some important properties. It is restricted in 1st and 3rd quadrant and it has only one point, a zero crossing point, where both current and voltage are zero.

Figure 2.2 shows an example of memristor's characteristics in  $q - \varphi$  and in i - v plane. The  $q - \varphi$  curve satisfies all three criteria and it has an initial point  $(q_0, \varphi_0)$ . Memristance at point P is a charge derivative of  $\varphi(q)$ . The pinched hysteresis which is shown in i - v plane is symmetric and has a zero crossing point at the origin. At P is the memristance at

**Figure 2.2:**  $q - \varphi$  and i - v relations of memristor. Adapted from [1].

instantaneous time  $t_a$  which is exactly the same as instantaneous resistance. Resistance R(i) = dv(i)/di can be calculated by taking a derivative from the i-v curve at point  $(i_a, v_a)$ . Memristor's output can not be predicted by looking at it's i-v curve only. Memristor's response is defined by it's  $q-\varphi$  curve uniquely and it's state depends on charge that has passed through it.

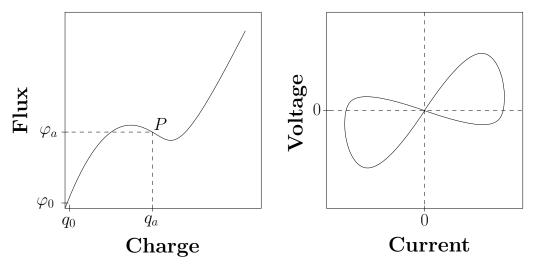

If one of the criteria is not fulfilled a component would no longer be a memristor. An another example is shown in Figure 2.3. In this case the  $q - \varphi$  is unique, non-linear, continuously differentiable but not increasing. At P the memristance M(q) < 0 which makes the i - v curve to spread in all four quadrants and there exists three v = 0 crossing points. This means that a memristor is no longer passive because such i - v curve is only formed when some internal power source is included.

**Figure 2.3:**  $q - \varphi$  and i - v relations of non-memristor. Adapted from [1].

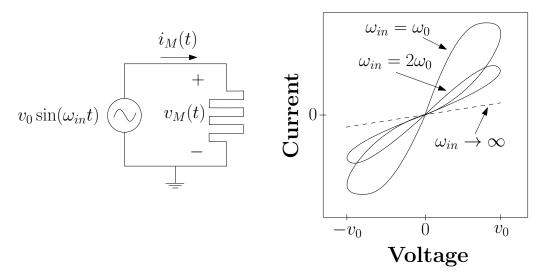

**Figure 2.4:** Frequency response of memristor. Voltage and current axis are swapped in this figure and subsequent figures to be consistent with existing literature.

The pinched hysteresis loops' waveforms are directly related to input signal frequency. A simple schematic is demonstrated in Figure 2.4 where a memristor is driven by an input  $v(t) = v_0 \sin{(\omega_{\rm in} t)}$ , with amplitude of  $v_0$  and angular frequency  $\omega_{\rm in}$ . Alternating voltage over memristor at time t is  $v_M(t)$  and alternating current through memristor is  $i_M(t)$ . When input signal's frequency approaches to zero,  $\omega_{\rm in} \to 0$  in other words signal has only dc-value, memristor will eventually saturate to act like a linear resistor. The situation is similar when  $\omega_{\rm in} \to \infty$ . The memristor degenerates to a linear resistor but with different resistance value than it is in dc-input's case which is mathematically proved in [4]. Infinitely fast alternating voltage does not allow magnetic flux to change its value because time over one signal period becomes infinitely small. The resistance values depends on a process and materials used on manufactured memristor but basically every ideal memristor will have two limiting memristances,  $R_{\rm ON}$  and  $R_{\rm OFF}$ . The frequency response of memristor shows behaviour where increasing frequency "tightens" hysteresis loops. The i-v curve shows that there are two linear stages between the "transition arcs". These states are typically referred in literature as on-resistance,  $R_{\rm ON}$  and off-resistance,  $R_{\rm OFF}$ , where  $R_{\rm ON} < R_{\rm OFF}$ . [5]

The mathematical definition of memristor presented in this chapter differs very much from real devices. Real memristor do not necessarily have clean pinched hysteresis curves in i-v plane or they are not categorized as true flux-charge memristors. The manufactured devices belong to a totally different subset than memristor in memristive systems. There is ongoing debate in scientific field whether manufactured memristors are real memristors

or are they part of some broad class of resistive systems. One paper published on Nature argues that memristors are impossible to manufacture in real world without using magnetic induction [7], and it may be possible that real memristor will be found in other physical structures than thin-film structures. Chua's mathematical definition is not under criticism but there exists disapproval against HP's device and other thin-film structures because they lack magnetic flux property, yet they are referred as memristors.

Existing literature mixes up terms memristor and memristive systems repeatedly. In this thesis term *memristor* is used although the device does not necessarily meet all the mathematical criteria that is set to it.

# 3 Physical Realization of Memristor

This chapter gives a brief overview of mechanisms behind resistive switching phenomenon as they are necessary to understand the behaviour and material choices of resistive switches. First, a short introduction of the history behind the switching observations and the HP's memristor model is presented. Further sections should give the basic idea of different switching types and models. Especially the redox-based effects behind resistive switching mechanisms are explained.

There may be a misconception in public that HP's device was the first memristor manufactured. Actually the resistive switching phenomenon was already reported in the 1960s. Some metal oxides such as NiO [8], and  $Ta_2O_5$  [9], were reported to have forming process produced by electrical field and after forming they showed switching properties with two different resistance levels and some memory effects. However, those devices were not robust enough to have any practical use and it took many decades until the interest on resistive switching rouse again among scientific field.

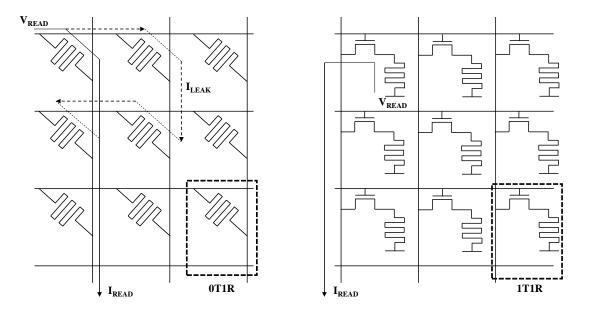

In the early 2000s there were more successful attempts to manufacture resistive switches. Materials like NiO [10], and TiO<sub>2</sub> [11], showed very promising switching properties. In 2002 Sharp published a paper [12], where they presented their colossal magnetoresistive (CMR) device that was manufactured using 0.5 µm complementary metal-oxide-semiconductor (CMOS) process. Sharp's memory architecture was a 64-bit array where the memory component was connected in series with a transistor or diode. These configurations are called one-transistor-one-resistor (1T1R) and one-diode-one-resistor (1D1R) correspondingly. The memory cell showed resistive switching when 3 V voltage pulse for programming and erasing was applied. Write and erase times were reported to be 20 ns and 10 ns while peak operating current was 200 µA. Using different pulse widths Sharp's researchers noticed that the device was able to have multiple resistance states which could be used in multi-bit storage. However they did not publish any information of endurance or retention

time. Sharp referred their device as resistance random access memory (RRAM) which was the first publication to use this term.

A small breakthrough was also made in 2004 when Samsung published a paper about their resistive memory [13]. Samsung accomplished to manufacture a NiO memory cell on 0.18 µm CMOS process using a 1T1R structure. They referred their memory structure as transition metal-oxide resistive random access memory which was shortened to OxRRAM. Samsung made memory technology oriented tests to their device where they showed that voltage pulses were necessary to switch from low-resistance state (LRS) to high-resistance state (HRS). They used operating voltage below 3 V and controlled current of 2 mA while running 10<sup>6</sup> set/reset cycles and 10<sup>12</sup> read operations. However Samsung had problems with failing endurance after one million set/reset operation. Also their high temperature baking test resulted many defunct memory cells mainly due soft errors. It is interesting to note that none of the papers about resistive switching did not refer to the original memristor paper. Maybe this was because Chua's papers were full of complex mathematics and his interests did not meet with experimental material scientists.

In 2008 HP Labs finally connected the dots and manufactured a device which they referred as a memristor. Their sandwich like structure used two platinum electrodes between titanium dioxide insulator. It was a beginning of multiple thin-film memristor implementations using different electrode and oxide materials. However it is impossible to give a single comprehensive equation or explanation of how thin-film memristor works because it's switching behaviour is dependant on not only materials used but also their combination [3].

In the next section HP's thin-film memristor is presented because it was the first to connect memristor theory to experimental observations that resulted multiple publications<sup>1</sup> from many research groups that observed resistive switching in metal-oxide nano structures.

# 3.1 HP's Device Model and Physical Properties

HP Labs presented their physical model of their two terminal memristor-like device in [2]. The first mathematical model of their device is very simple and some improved and more

<sup>&</sup>lt;sup>1</sup>Search report from *Web of Science* (http://apps.webofknowledge.com) results 936 articles between years 1971-2007 and 14902 articles between years 2008-2015 using keywords "memristor OR memristive OR resistive switching".

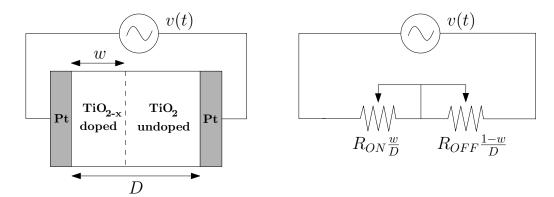

complex modelling equations have been presented and studied [14,15]. HP's model is presented in Figure 3.1. External sinusoidal voltage  $v(t) = v_0 \sin{(\omega_{\rm in} t)}$  changes the boundary area between doped and undoped regions. Strukov et al. [2], tried to induce mathematical model of their device which would match Chua's definition for memristive systems. They obtained the following equations

$$v(t) = \left(R_{\rm ON} \frac{w(t)}{D} + R_{\rm OFF} \left(1 - \frac{w(t)}{D}\right)\right) i(t)$$

(3.1)

$$\frac{dw(t)}{dt} = \mu_V \frac{R_{\rm ON}}{D} i(t) \tag{3.2}$$

where D is the width of oxide material,  $\mu_V$  is average ion mobility and formula for w(t) is

$$w(t) = \mu_V \frac{R_{\text{ON}}}{D} q(t). \tag{3.3}$$

Equations (3.1) and (3.2) are modifications of equations v = R(w)i and  $\dot{w} = f(w,i)$ . Because  $R_{\text{ON}} \ll R_{\text{OFF}}$  it follows that inserting w(t) to (3.1) following approximation is obtained

$$v(t) = R_{\text{OFF}} \left( 1 - \frac{\mu_V R_{\text{ON}}}{D^2} q(t) \right) i(t). \tag{3.4}$$

These equations show that HP's device belonged to group of resistive systems. They had to show that their device was memristor and it should also have charge dependent memristance. This was indeed the case because memristance can be written in the form v(t) = M(q(t))i(t) which results memristance equation

$$M(q(t)) = R_{\text{OFF}} \left( 1 - \frac{\mu_V R_{\text{ON}}}{D^2} q(t) \right). \tag{3.5}$$

It is true that previous equations lack direct connection to magnetic flux that was crucial in defining a memristor. Because there were no clear indications of magnetic fields inside small resistive switching components it was hard for researchers to intentionally manufacture memristive devices. This confusion can be avoided by using a term flux linkage instead of magnetic flux as both equations are defined exactly the same in (2.5). Magnetic flux's physical explanation is  $\varphi_B = B \cdot S$  where magnitude of magnetic field B passes through surface of vector area S. Flux linkage does not represent any physical magnetic field but only a time integral over voltage.

HP's model assumes that  $R_{\mathrm{OFF}}$ ,  $R_{\mathrm{ON}}$  and D are independent of q and t, which may

Figure 3.1: A simplified model of HP's memristive device shows a sandwich structure where width of  $TiO_{2-x}$  doped area defines the state variable w. A circuit equivalent is shown on the right where two variable resistances  $R_{ON}$  and  $R_{OFF}$  represent materials  $TiO_{2-x}$  and  $TiO_2$  respectively.

not be the case in practise. Also HP's claim of memristor discovery led their first model to define memristive behaviour rather than explaining physical mechanisms behind phenomena.

A state variable w in the model has more limited range than Chua's mathematical definition where  $\mathbf{w} \in \mathbb{R}^n$ . Theoretically, a state variable that is a width of doped region could only vary between platinum electrodes in other words  $w \in [0, D]$ . It is proportional to q that passes through TiO<sub>2</sub> region.

A brief physical explanation of how resistive switching happens in  $TiO_2$  is presented in this section. At the time when HP was doing experiments on their device using micro-scale and nano-scale devices they noticed that memristance was more noticeable in very small structures. Because any real component e.g. resistor or capacitor also have parasitics inside them (such as parasitic resistances or parasitic inductances) it may be possible that they contain parasitic memristances also. However this parasitic element is undetectable in large scale devices which made the discovery of memristor to be a very difficult task. As electrical devices started to shrink in size, memristance became more noticeable. There are papers which misinterpreted memristance as tunnel effect [9], or anomalous capacitance [16]. Currently, memristance is known to be a dominant element in nano-scale thin-film metal-oxide structures. In theory, a memristance in nanometer devices is one million times larger than in micrometer devices. This happens because a memristance e.g. in  $TiO_2$  devices has a factor of  $1/D^2$  as shown in simplified model in (3.5).

Strukov and Williams investigated switching speeds of Pt/TiO<sub>2</sub>/TiO<sub>2-x</sub>/Pt device [17]. In their model the motion of atomic particles caused the resistive switching. Charge carriers could be ions, molecules or vacancies. Even relatively small non-stoichiometric of

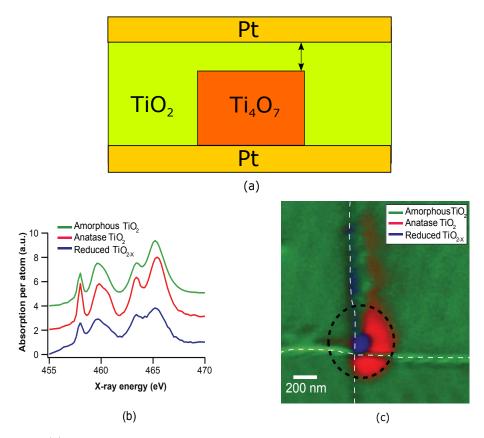

**Figure 3.2:** (a) A simplified cross cut of the device which shows  $Ti_4O_7$  channel. Resistance switching happens when this channel is modulated using electric field. (b) X-ray absorption spectrum revels three different materials present in device. (c) Colour mapped STXM image of the device shows the formation of conductive channel. Partially taken from [18].

0.1 % in  $TiO_{2-x}$  which is equivalent approximately  $5 \cdot 10^{19}$  dopants/cm<sup>3</sup> makes the oxygen deficient layer highly conductive [15].

The first manufactured devices used a electroforming step to create a conducting channel in TiO<sub>2</sub> region. Strachan et al. studied [18], forming process and material changes inside the device. Before the forming step the device showed strong rectifying behaviour that could be interpreted as Schottky like contacts at bottom and top interfaces. It turned out that after initial forming step there exists a 10 nm to 200 nm wide channel that would form in a random location inside TiO<sub>2</sub>. Researchers probed TiO<sub>2</sub> region with x-ray absorption spectroscopy. The spectrum, which is shown in Figure 3.2, revealed three different phases or sub-oxides of titanium dioxide and the width of conducting channel. Spectral analysis revealed that the material in conducting channel was actually a sub-oxide of TiO<sub>2</sub>. Transmission electron microscopy (TEM) of reduced TiO<sub>2-x</sub> region showed that the diffraction pattern figure was the same as the crystal form of Ti<sub>4</sub>O<sub>7</sub> which is also known as Magnéli phase. The on-off switching happens when the width of region between

Ti<sub>4</sub>O<sub>7</sub> and Pt changes. This modulation which is only in range of couple nanometer causes significant changes in resistance in spite of the fact that the conducting channel is never fully shorted with electrode. A scanning transmission x-ray microscope (STXM) analysis of the device showed that the formed channel had an approximate width of 100 nm which is color mapped in STXM image in Figure 3.2. The resistive switching mechanism of TiO<sub>2</sub> was confirmed by other independent groups especially Kwon et al. [19]. They concluded that increasing concentration of oxygen vacancies would result strong Joule heating effect and high temperatures drive thermodynamic forces to form the Magnéli phase.

# 3.2 Resistive Switching

When knowledge and observations of resistive switching mechanisms and materials increased, one can argue, that the terms memristance and memristor are good for explaining and defining all the discovered devices. Many times the pinched hysteresis curves are far from being clear and beautiful "butterfly" or "bow-tie" shaped figures. In some devices the pinched hysteresis in two different quarters of i-v plane is totally missing because the switching happens only on positive voltage. However, the fact is that currently new devices and materials are researched extensively and part of this happened because there was an attempt to discover the Chua's fundamental circuit element. Some papers might still refer Chua's 1971 paper but nowadays many authors do not find it necessary as their device and research is more concerned to have use in practical applications instead of proving Chua's theory of postulated memristor. The term resistive switching is often used in literature and it is in many cases more illustrative word for the whole phenomenon.

As noted previously, a single comprehensive equation or model that would explain the behaviour of all different thin-film devices is practically impossible. Resistive switching does not only depend on materials that are used but it is also dependent on their different combination [3]. Resistive switching behaviour can be classified into two different types: unipolar or bipolar.

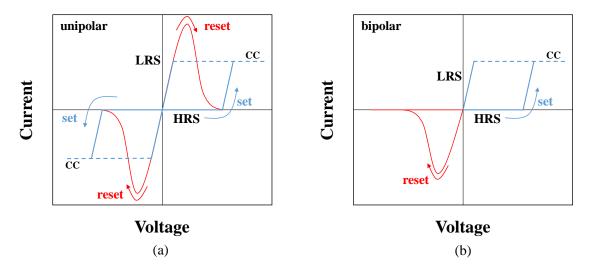

In unipolar (or non-polar) case, resistive switching happens when amount of applied voltage (or current) exceeds certain level. This means that change from HRS to LRS which is also called as *set* phase and correspondingly the change from LRS to HRS which is called *reset* phase happens in the same voltage polarity. In bipolar switching setting and resetting mechanism does not only depend on amplitude but also polarity of applied

**Figure 3.3:** The i-v curves of (a) unipolar mode and (b) bipolar mode. In unipolar mode it is possible to change device state between HRS and LRS with both negative or positive voltage. In bipolar mode only the opposite polarity of voltage have the effect of state change. In both cases the current is limited by the compliance current (CC).

voltage. For example, set phase happens on positive voltage when amplitude reaches certain level. Applying increased positive voltage would not cause any change in device's resistance state. However, a subsequent negative voltage will cause a change in device thus resetting it back to its previous state. Figure 3.3 shows the typical i-v curves of two switching modes. Some devices may have the set happening on negative voltage and reset on positive voltage and the curves may be far from being clean hysteresis curves. They are more likely to be distorted or "noisy" between different cycles, so this figure is only used to present and give the understanding of basic behaviour.

Typically a fresh sample of manufactured device has some *initial resistance* which might be different from the resistance states that are present after applying multiple switching cycles [3]. The initial resistance state might need a higher voltage to trigger resistive switching behaviour in device. This is usually called a *forming voltage* and the phenomenon is referred in literature as *forming* or *electroforming*.

The initial forming and following set phases are usually very fast and abrupt processes so it is necessary to prevent device breakdown by limiting the current when device changes it's state to LRS. The *compliance current* is achieved having a transistor, a diode or another resistor in series with resistive switching component. If the manufactured device lacks the mentioned components, compliance current is provided by measurement devices like semiconductor parameter analysers or other corresponding equipment. However, in some cases the switching time is so fast that measurement equipment is not fast enough

**Figure 3.4:** Classification of resistive switching mechanisms based on physical driving forces. Unipolar and bipolar operation of resistive random access memories are typically associated with three redox based mechanisms: ECM, VCM and TCM. Adapted from [20].

to react to set process and in such cases the device may break down unintentionally.

Some external ambient conditions such as temperature have also effect in resistive switching. Even the fabrication conditions and process have some effect because the structure of metal-oxide material is never totally ideal and uniform. Possible methods to manufacture oxide based devices include reactive sputtering, pulse laser deposition (PLD), and atomic layer deposition (ALD). Especially the ALD shows promising results because it has an ability to control the uniformity and thickness of the oxide film which reduces the variance between devices as well as variability in single device. [3]

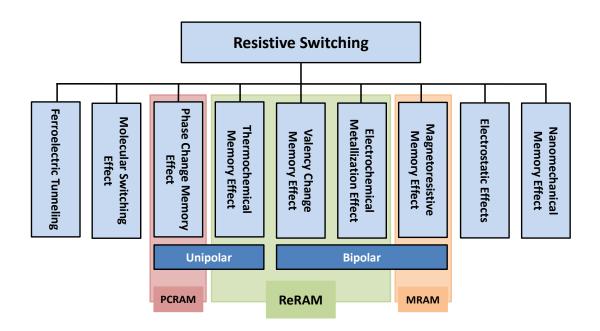

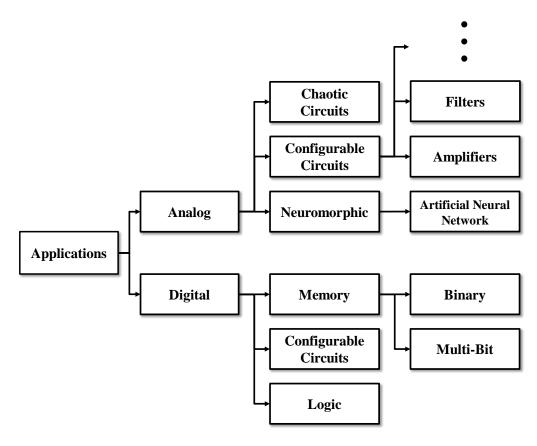

A large variety of different physical phenomena are observed that lead to resistive switching. Waser et al. presented a very comprehensive review [20], where different switching mechanisms are divided into nine categories that are shown in Figure 3.4. Some of the physical driving forces are related to unipolar switching while others contribute to bipolar switching. Waser's paper focused on redox-related chemical effects that are typically associated with resistive random access memories (ReRAM). A more recent review

about switching mechanisms was introduced by Pan et al. [21], where they focused on ion migration, charge trapping and thermochemical reactions in inorganic and also organic materials. Different switching mechanisms are utilized in different memory technologies such as phase change random access memory (PCRAM) or magnetoresistive random access memory (MRAM). Redox (reduction-oxidation) based mechanism include electrochemical metallization effect (ECM), valency change memory effect (VCM) and thermochemical memory effect (TCM). These effects are explained in Section 3.4.

# 3.3 Filamentary and Interface Type Switching Models

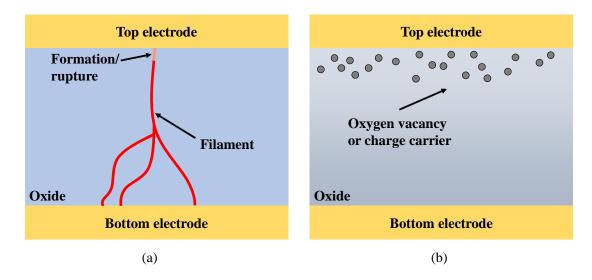

In previous section it was mentioned that resistive switching can be classified into two different categories, unipolar and bipolar. The type of conducting path can also be categorized into two types. The proposed models for switching are filamentary type conducting paths and interface type conducting paths. The general thumb-of-rule link between conduction path and switching behaviour is that the conduction filament can be associated with both types of switching behaviour but interface-type mechanism is typically related only to the bipolar switching behaviour [22]. In Figure 3.5 these two models are shown. However, the details of resistive switching are still missing a comprehensive explanation and it is an active research area. Many different research groups have attempted to see what happens inside the device during switching [18, 19, 20, 23, 24, 25, 26].

#### 3.3.1 Filamentary Type Model

Basically, in filamentary type model the forming process happens when a soft electric breakdown happens in oxide material between cathode and anode. Soft breakdown means that this condition can be reversed even though not fully because in many cases the first forming is reported to require higher voltage than following set forming steps. The filamentary switching process is basically divided into three different sections: forming, set and reset.

Filamentary type switching can be also recognized by it's "fingerprint" of area independence. This means that increasing (or decreasing) device area has almost no effect on the ratio of on-resistance and off-resistance. A simple explanation for this is the formation of single filament during set process. Formation of filament can happen anywhere in ox-

**Figure 3.5:** Simplified models for (a) filament conduction paths and (b) interface-type conduction paths. Adapted from [22].

ide material and if the filament is expected to be have the same "strength" in consecutive forming, the conducting current is also expected to be the same thus having any noticeable effect on on-resistance value. Increasing device size does not matter if only one filament is allowed to form. In reality, filament's geometry is never identical between consecutive switching cycles. Precise control of filament structure is not a trivial task because of the stochastic nature of filament formation. This is the main reason why i-v curves of manufactured device have high statistical variability between switching cycles.

The oxide thickness is proportional to forming voltage in filamentary type switching. If oxide thickness is reduced strong electric field is not necessary to form a conducting channel in oxide. In most devices the oxide thickness is in scale of nanometers. The dependence between forming voltage and oxide thickness is mostly reported to be linear. Because the initial forming voltage is typically higher that following set voltages, researchers began to question if it is possible to manufacture forming free devices. Reports of forming free devices exists e.g. Lee et al. [27], succeeded to manufacture a 3 nm oxide thickness in  $HfO_x$  device that did not require initial forming. Fang et al. [28], showed a multilayer  $HfO_x/TiO_x$  structure without need of initial forming.

Some models assume that there exists only one conducting filament. This may be possible in some transition metal oxides where the first forming filament is responsible for conducting all electrical current. Still experimental data suggest that there may be hints of multiple filament formations. If multiple filaments are formed the device would also

have multiple resistance states instead of two: on-resistance and off-resistance. This kind of behaviour is beneficial in memory technologies where single device could store multiple bits. Formation of multiple filaments can be achieved using e.g. multiple compliance current levels. Higher current would form several filaments, although rupturing those filaments is usually an uncontrollable process. Repeatability is also an issue when reliable behaviour is necessary but many times the single filament devices suffer from these issues too. The filament breakdown should happen sequentially during voltage sweep in discrete manner. Ideally, the voltage levels where the rupture happens, should be same between sequential sweeps [29]. Multiple resistance states are also possible to achieve with single filament when the size of theinter filament is changed by precise voltage control. In this case the controllable resistance states are hard to achieve because the resistance switching phenomena is highly non-linear. However, if small changes in filament size can be controlled, there is a possibility to achieve pseudo-analog resistance levels.

The conducting filaments in transition metal oxides involve e.g. oxygen vacancy transport. Studying the filament may show defects in local oxygen content as it is shown in [19]. This explains the reason why transition metal oxides are good candidates for resistive switching devices. They have at least two oxidation states and they are good ionic conductors. In unipolar switching the forming process creates a filament consisting of oxygen vacancies. During reset process oxygen atoms fill the vacancies in filament thus breaking it. This model is limited as it does not take into account any electrode materials. The switching needs an active electrode e.g. platinum or copper. In this case, models assume that active electrode catalyses oxidation near the electrode interface. The filament rupture does not happen in the middle of oxide material as the pure oxygen vacancy models indicates. The bipolar switching needs asymmetric structure to operate that is achievable using only one active electrode material (which is also the case in unipolar switching) or using cells with non-uniform built-in oxygen vacancies. The active electrode, typically anode, acts as an oxygen reservoir in forming as oxygen ions drifts towards the electrode thus creating an interfacial layer. In reset, the oxygen ions recombine with the vacancies or oxidize the metal back to high resistance state. This model which was proposed by Yu et al. [30], to be consistent with unipolar and bipolar cases. However, as Wong noted in his review paper [3], the model should be viewed only as a phenomenological description of experimental observation and there exists alternative theories. A more comprehensive review about filament formation and physical processes are given in Section 3.4.

# 3.3.2 Interface Type Model

Interface type conducting path model is typically used in complex oxide materials such as doped perovskite oxides. Perosvkite complex metal oxide means a material that has similar crystal type structure than calcium titanium oxide CaTiO<sub>3</sub>. As the opposite of filamentary type switching in interface type switching the resistance is expected to be area dependant. This idea can be explained in a simple way because the switching happens in the whole interface that exists between electrode material and oxide material, and thus the resistance depends on the device area. The interfacial switching in perosvikte oxides was studied by Sawa [22]. He made an assumption that the possible origin of resistive switching is the Schottky barrier because the device has a capacitor like structure and the resistance can be changed applying an electric field over it. The switching is an outcome of Schottky barrier modulation. Modulation moves oxygen vacancies towards or away from the interface. Other proposed models that involve e.g. electrochemical migration of oxygen vacancies or trapping of charge carriers are presented in 3.4.

Sawa noticed that some materials would allow resistive switching but changing anode material would lead to non-linear resistor behaviour. This dependence make it more evident that Schottky barrier is indeed the probable cause of contact resistance. For example, a cell made from  $Ti/Pr_{0.7}Ca_{0.3}MnO_3$  (shortened to Ti/PCMO) would lead to resistive switching while Au/PCMO showed no switching behaviour. It can be assumed that characteristics of switching depend on electrical properties and some studies would confirm that by modifying the interface properties e.g. using different doping levels of charge carriers. If the amount of charge carriers are reduced by annealing a cell made of Ti/PCMO at 670 K in air or  $O_2$  atmosphere, curves in i-v plane did not show any hysteresis. Finally Sawa noted that the p-type and n-type materials have opposite properties. In n-type material oxygen vacancies act as donors and in p-type material they are acceptors. He concluded that electrochemical redox reaction may indicate that oxygen vacancies are important factor in interface-type switching mechanism. [22].

Interfacial type switching is not only observed in perovskite materials but also in simple binary oxides although the mechanism in latter is supposed to be simpler. For example Yang et al. [31] manufactured  $\text{Ti/TiO}_2/\text{Pt}$  device where  $\text{Ti/TiO}_2$  contact is ohmic and  $\text{TiO}_2/\text{Pt}$  is Schottky type. The negative voltage applied to platinum anode drifts oxygen vacancies towards  $\text{TiO}_2/\text{Pt}$  interface thus reducing the width of interface. Applying a

positive voltage would have an opposite effect. The same is true also in perosvkite materials as the charging effect at the interface also plays an important role [32].

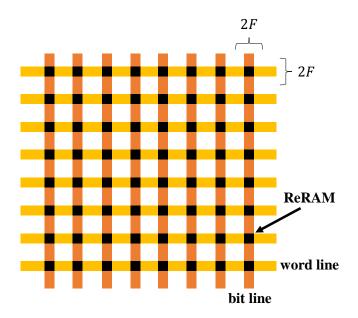

There are some disadvantages for interfacial type switching compared to filament type switching. The biggest downside is the necessity of complex perovskite oxide that may not be compatible with CMOS manufacturing process. Also the noble metal platinum is needed for a good Schottky barrier. Interfacial type devices have thicker oxide material than filamentary type devices. This may have some problems in future when scaling becomes more relevant. However, there are also some advantages as asymmetric behaviour and non-linearity in i-v plane allows operation of self-rectifying cell. Self-rectifying resistive switch acts itself as a diode thus removing the need for an external component. This is very beneficial in traditional memory arrays and also in 3D stacked memories [32]. Memory architectures using resistive switches are discussed more detail in Section 4.3.

# 3.4 Redox-Based Switching Mechanisms

## 3.4.1 Electrochemical Metallization Effect

In electrochemical metallization systems a conductive bridge (or channel) is formed between electrode materials where one electrode is electrochemically active metal and other electrode is electrochemically inert counter. Material between electrodes is a solid electrolyte. A very basic explanation of switching from HRS to LRS happens when active electrode metal, which is denoted as M, dissolutes according to,  $M \to M^{a+} + ae^-$ , where  $e^-$  is electron and a is positive charge in  $M^{a+}$  cation. Migrations of cations happen under high electric field in electrolyte material before an electrocrystallization occurs on the surface inert electrode,  $M^{a+} + ae^{-} \rightarrow M$ . The metal filament is broken when voltage that has reverse polarity is applied thus making the previously explained process to happen backwards. Some cations still remain in electrolyte so the device actually never returns to initial state like it was before the first forming step. This is the probable reason that initial forming voltage is higher than consecutive set voltages because no M<sup>a+</sup> cations are present in fresh device. Some of the most typical electrode materials that are involved in ECM effect are Cu and Ag. Electrolyte materials such as SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> or a-Si have large conductivity of the electrode cations. A very detailed analysis of fundamental processes behind electrochemical metallization memories was given by Valov et al. in [33].

ECM effect is also associated in literature with programmable metallization cells (PMC)

and especially conductive bridge random access memories (CBRAM). The term CBRAM has become a registered trademark but it is still used widely in academic literature. It can be argued that CBRAM and ReRAM are different technologies but in this thesis, all redox-based reactions are summarized under the term ReRAM.

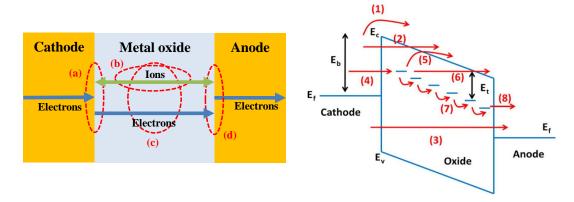

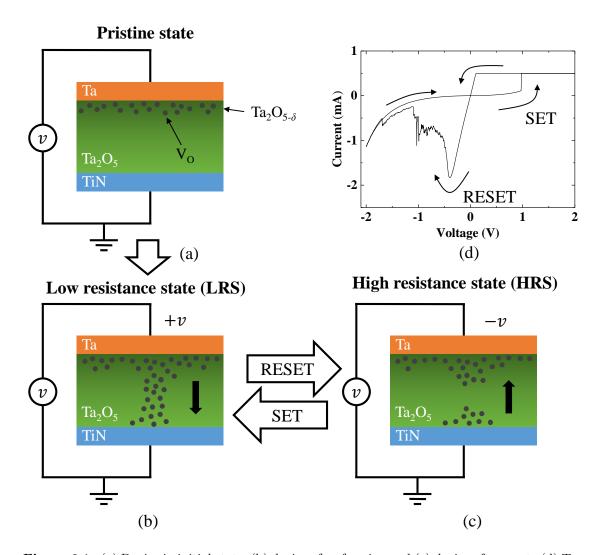

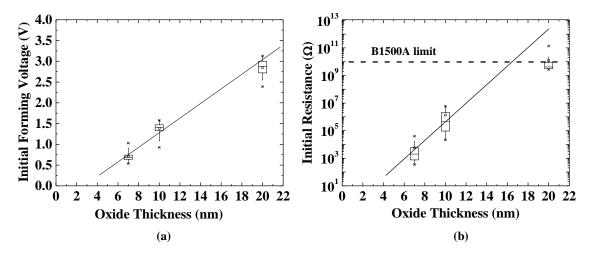

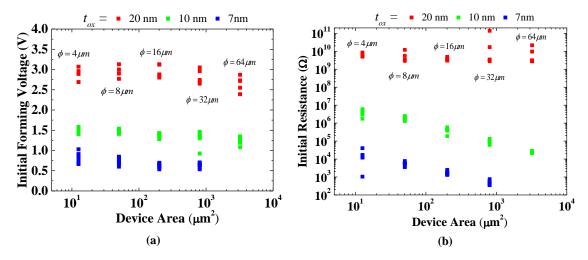

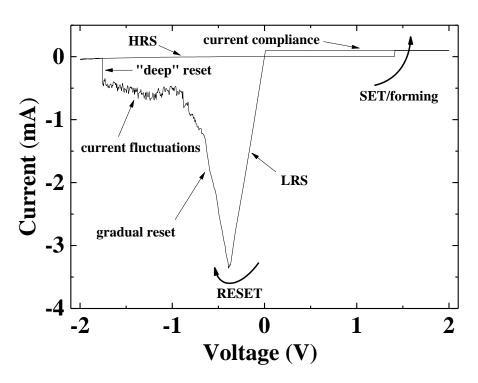

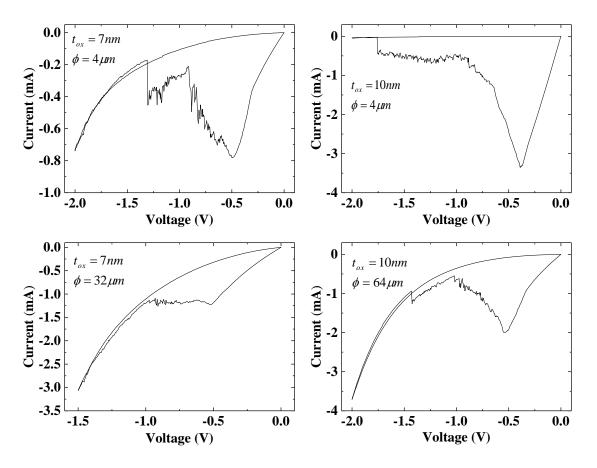

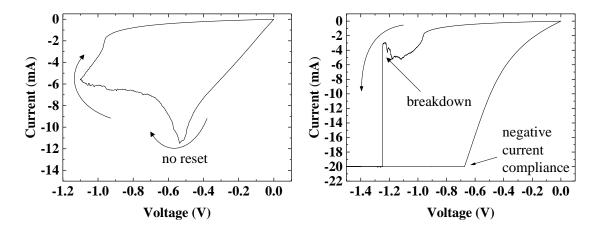

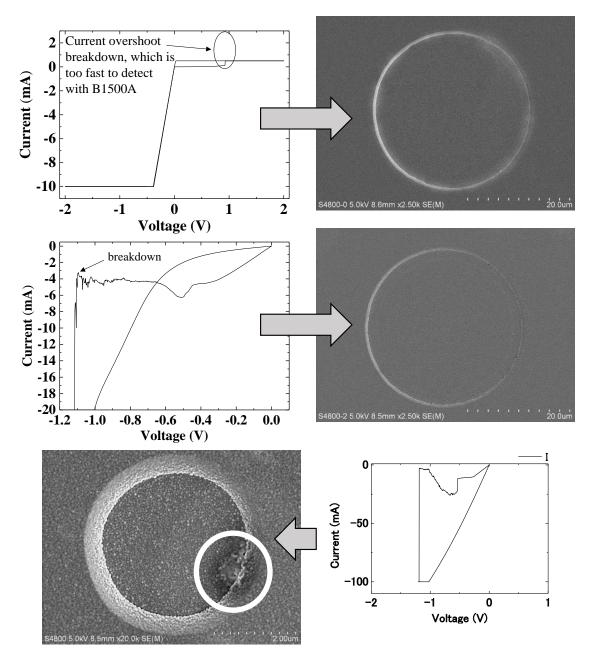

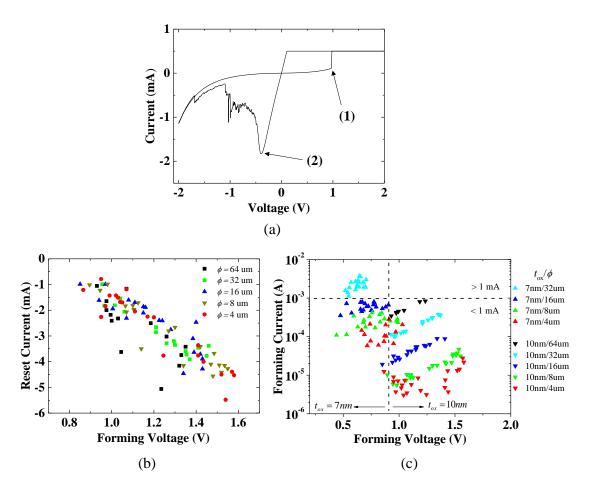

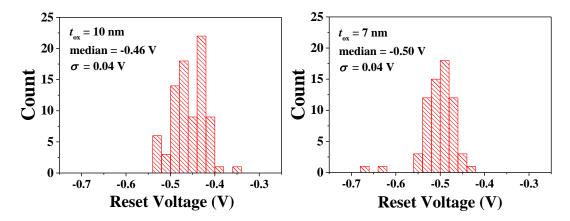

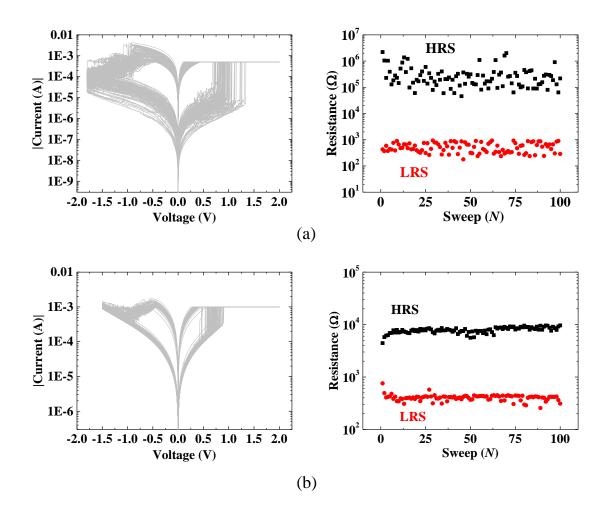

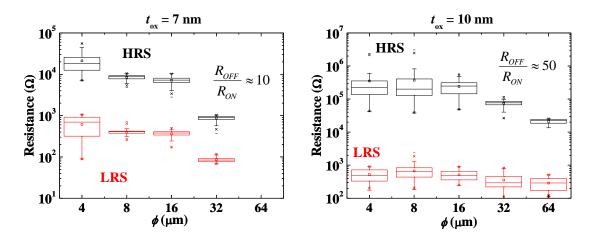

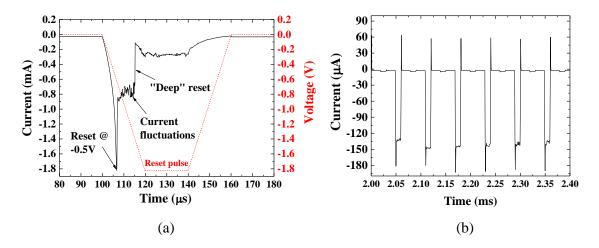

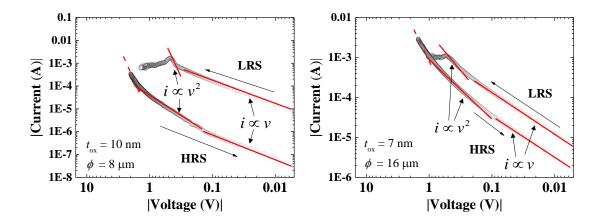

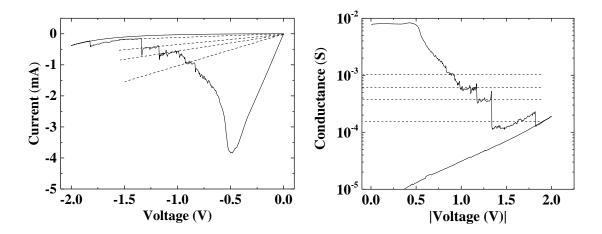

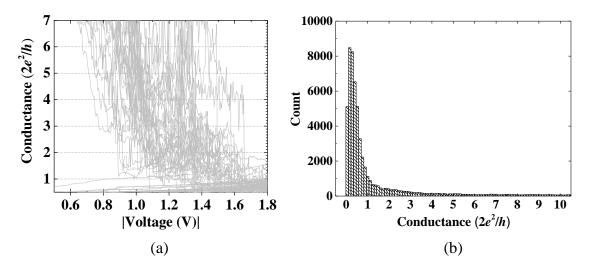

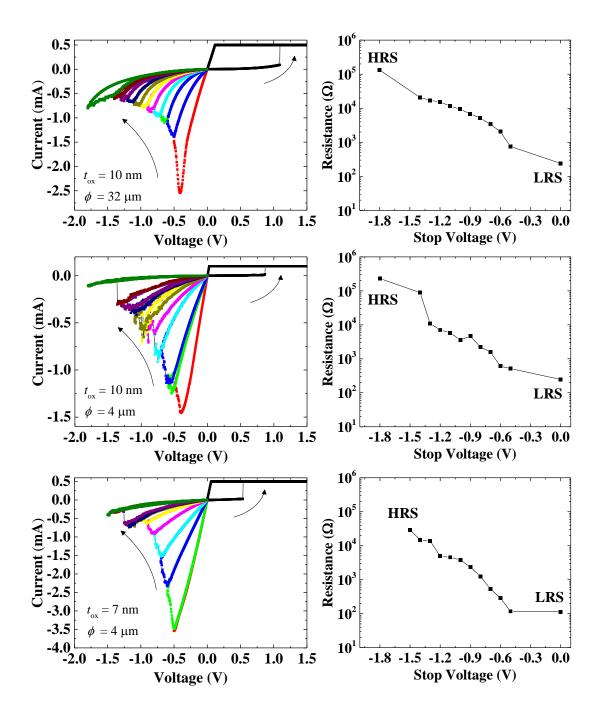

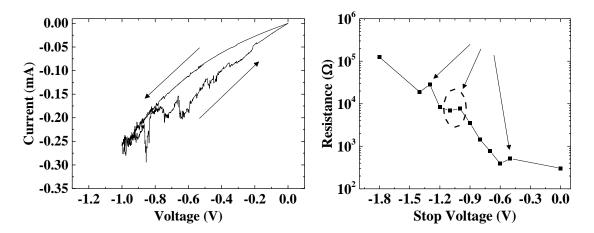

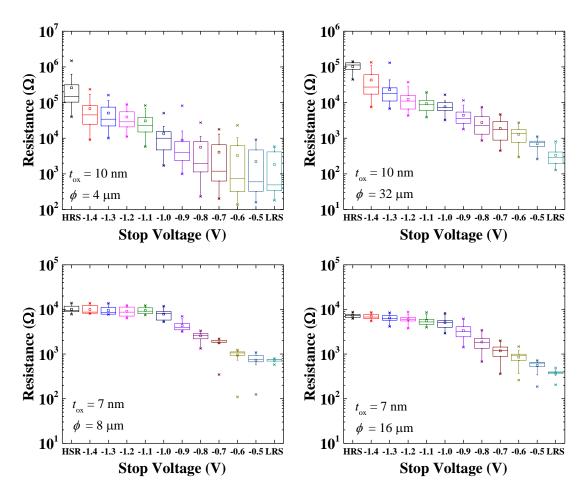

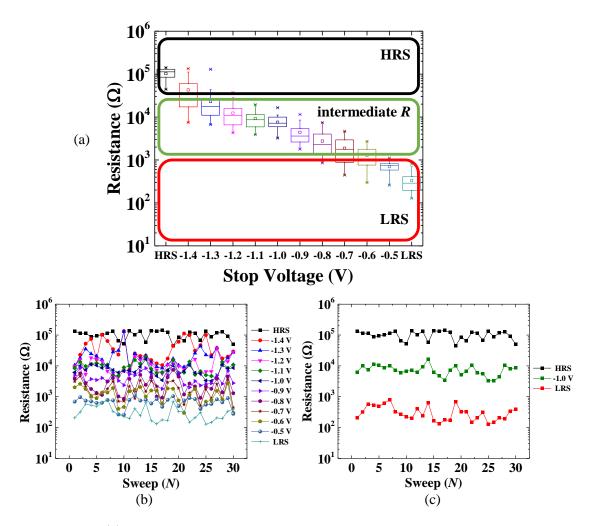

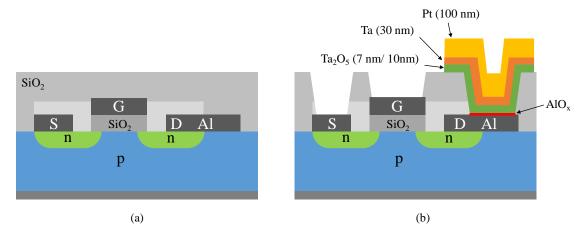

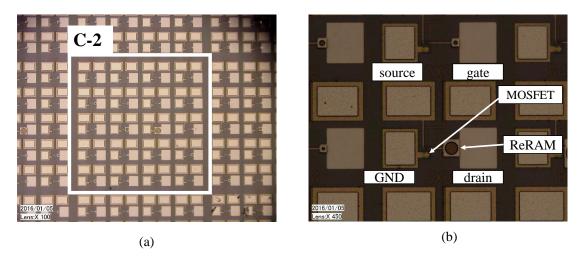

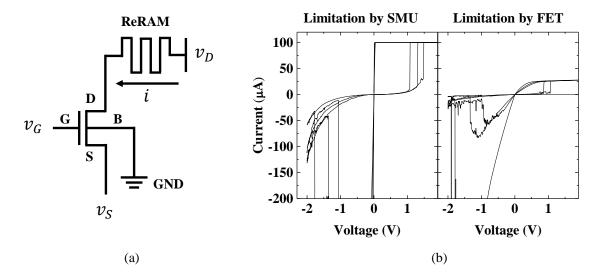

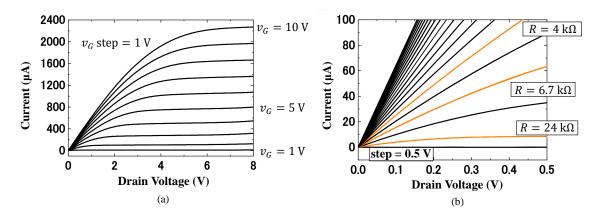

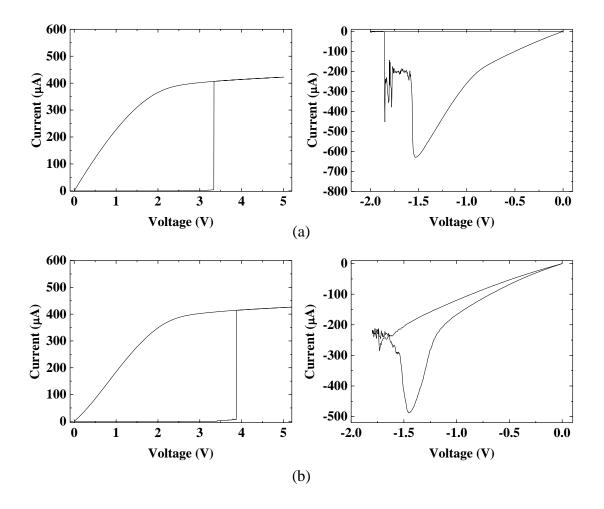

## 3.4.2 Valence Change Memory Effect